# 2. Digital Logic and Microprocessor

PANA ACADEMY

Er. Pralhad Chapagain

# Syllabus

- 2.1 Digital logic: Number Systems, Logic Levels, Logic Gates, Boolean algebra, Sum-of-Products Method, Product-of-Sums Method, Truth Table to Karnaugh Map. (AExE0201)

- 2.2 Combinational and arithmetic circuits: Multiplexetures, Demultiplexetures, Decoder, Encoder, Binary Addition, Binary Subtraction, operation on Unsigned and Signed Binary Numbers. (AExE0202)

- 2.3 Sequential logic circuit: RS Flip-Flops, Gated Flip-Flops, Edge Triggered Flip-Flops, Mater- Slave Flip-Flops. Types of Registers, Applications of Shift Registers, Asynchronous Counters, Synchronous Counters.

(AExE0203)

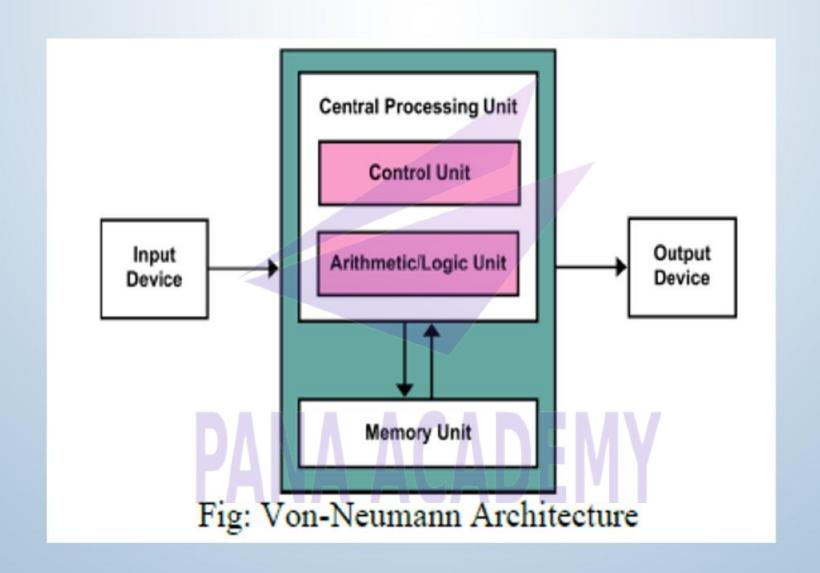

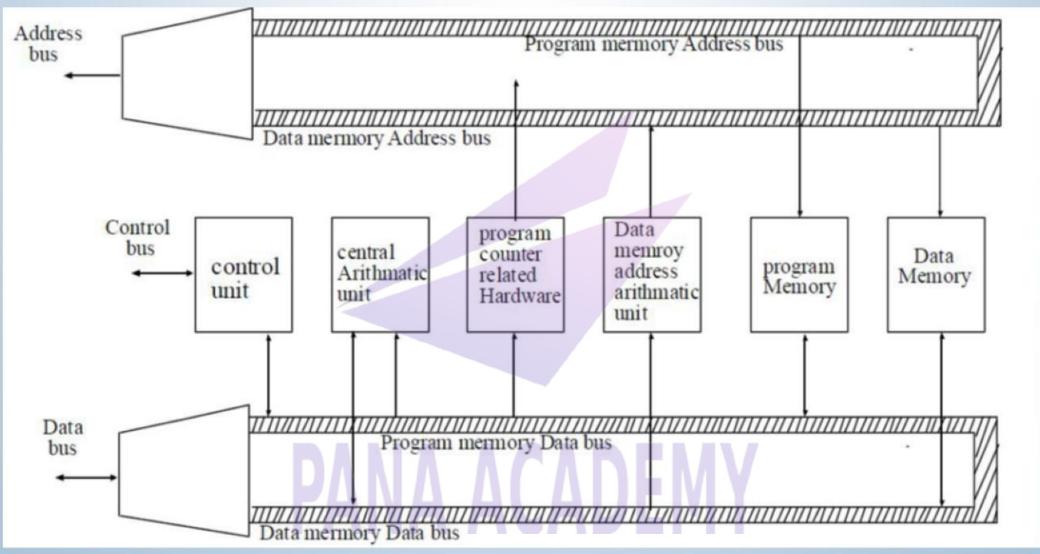

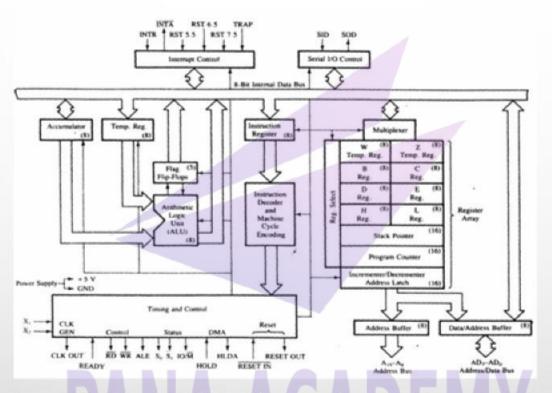

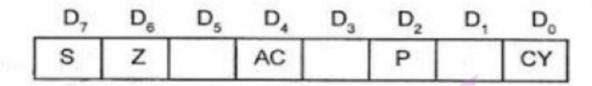

- 2.4 Microprocessor: Internal Architecture and Features of microprocessor, Assembly Language Programming. (AExE0204)

- 2.5 Microprocessor system: Memory Device Classification and Hierarchy, Interfacing I/O and Memory Parallel Interface. Introduction to Programmable Peripheral Interface (PPI), Serial Interface, Synchronous and Asynchronous Transmission, Serial Interface Standards. Introduction to Direct Memory Access (DMA) and DMA Controllers.

(AEXE0205)

- 2.6 Interrupt operations: Interrupt, Interrupt Service Routine, and Interrupt Processing. (AExE0206)

2.1 Digital logic: Number Systems, Logic Levels, Logic Gates, Boolean algebra, Sum-of-Products Method, Product-of-Sums Method, Truth Table to Karnaugh Map. (AExE0201)

# Number System

- Binary

- Octal

- Decimal

- Hexadecimal

Conversions

#### POSITIVE AND NEGATIVE LOGIC

#### **POSITIVE LOGIC:**

When we use binary 1 for high voltage and binary 0 for low voltage then it is called positive logic.

#### **NEGATIVE LOGIC:**

When we use binary 0 for high voltage and binary 1 for low voltage then it is called Negative logic.

Truth Table

| A | Y=A' |

|---|------|

| 1 | 0    |

| 0 | 1    |

Negative Logic NOT gate

Truth Table

| A | В | Y=A+B |

|---|---|-------|

| 1 | 1 | 1     |

| 1 | 0 | 0     |

| 0 | 1 | 0     |

| 0 | 0 | 0     |

Negative Logic OR gate

Truth Table

| A | В | Y=A.B |

|---|---|-------|

| 1 | 1 | 1     |

| 1 | 0 | 1     |

| 0 | 1 | 1     |

| 0 | 0 | 0     |

Negative Logic AND gate

- · Positive logic AND gate is equivalent to Negative logic OR gate and vice versa.

- Positive logic NAND gate is equivalent to Negative logic NOR gate and vice versa.

- Positive logic XOR gate is equivalent to Negative logic XNOR gate and vice versa.

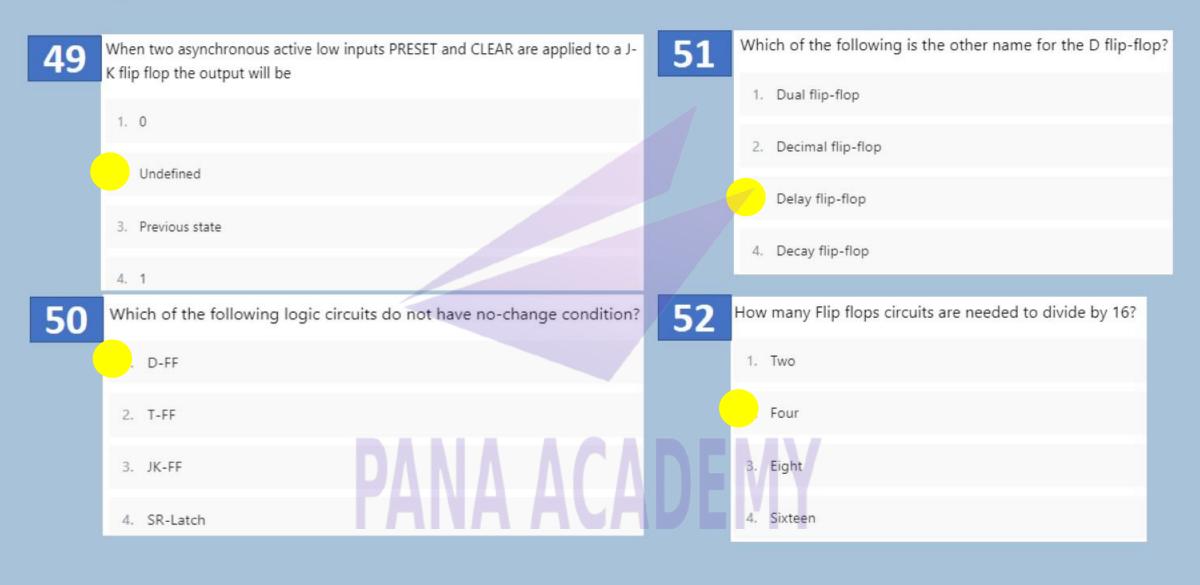

# Logic Gates

- Basic Gates (NOT, AND, OR)

- Universal Gates (NAND, NOR)

- Exclusive Gates (XOR, XNOR)

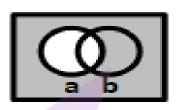

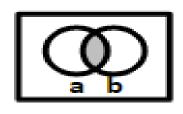

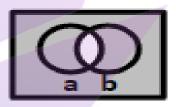

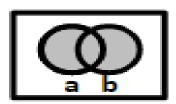

### **VENN** Diagram

**Buffer**

a

NOT

a

AND

ab

NAND

ab

OR

a+b

NOR

a+b

XOR

a⊕b

XNOR

a⊕ b

## Boolean Algebra

- Boolean Algebra is used to analyze and simplify the digital (logic) circuits. It uses only the binary numbers i.e. 0 and 1. It is also called as Binary Algebra or logical Algebra. Boolean algebra was invented by George Boole in 1854.

- Boolean Laws

#### Commutative law

Any binary operation which satisfies the following expression is referred to as commutative operation.

(i)

$$A.B = B.A$$

(ii)  $A + B = B + A$

# Boolean Algebra

#### Associative law

This law states that the order in which the logic operations are performed is irrelevant as their effect is the same.

(i)

$$(A.B).C = A.(B.C)$$

(ii)

$$(A + B) + C = A + (B + C)$$

#### Distributive law

Distributive law states the following condition.

$$A.(B+C) = A.B + A.C$$

#### AND law

These laws use the AND operation. Therefore they are called as AND laws.

(i)

$$A.0 = 0$$

(ii)

$$A.1 = A$$

(iv)

$$A.\overline{A} = 0$$

# Boolean Algebra

#### OR law

These laws use the OR operation. Therefore they are called as OR laws.

(iii)

$$A + A = A$$

(iv)  $A + \overline{A} = 1$

#### **INVERSION** law

This law uses the NOT operation. The inversion law states that double inversion of a variable results in the original variable itself.

$$\frac{-}{A} = A$$

### DE MORGANS THEOREM

#### Theorem 1

$$\overline{A.B} = \overline{A} + \overline{B}$$

NAND = Bubbled OR

#### Theorem 2

$$\overline{A+B} = \overline{A}.\overline{B}$$

NOR = Bubbled AND

FOR MCQ: https://www.sanfoundry.com/discrete-mathematics-questions-answers-de-morgan-laws/

#### **BOOLEAN ALGEBRA**

#### **Dual Theorem:**

- Starting with a Boolean relation, we can derive another Boolean relation, called its dual by the following steps:

- Changing each OR sign into AND sign

- Changing each AND sign into OR sign

- Complementing all 0's and 1's

#### Example:

| S.N. | Given Expression               | Dual of given expression   |

|------|--------------------------------|----------------------------|

| 1    | A + AB = A                     | A. (A + B) = A             |

| 2    | A + A'B = A + B                | A. (A' + B) = A.B          |

| 3    | $\mathbf{A} + \mathbf{A'} = 1$ | $\mathbf{A}.\mathbf{A}'=0$ |

| 4    | (A+B)(A+C) = A+BC              | A.B + A.C = A. (B + C)     |

#### STANDARD FORM AND CANONICAL FORM

#### **CANONICAL FORM:**

and primed if one (1).

- Max Term

- Min Term

#### **Max Term:**

• Each Max term is obtained from an OR logic of n variables with each variable being unprimed if

the corresponding bit is zero (0)

| A | В | C | Max term | designation |

|---|---|---|----------|-------------|

| 0 | 0 | 0 | A+B+C    | $M_0$       |

| 0 | 0 | 1 | A+B+C'   | $M_1$       |

| 0 | 1 | 0 | A+B'+C   | $M_2$       |

| 0 | 1 | 1 | A+B'+C'  | $M_3$       |

| 1 | 0 | 0 | A'+B+C   | $M_4$       |

| 1 | 0 | 1 | A'+B+C'  | $M_5$       |

| 1 | 1 | 0 | A'+B'+C  | $M_6$       |

| 1 | 1 | 1 | A'+B'+C' | $M_7$       |

12

#### STANDARD FORM AND CANONICAL FORM

#### **Min Term:**

• Each Min term is obtained from an AND logic of n variables with each variable being unprimed if the corresponding bit is one (1) and

primed if zero (0).

| A   | В | C | Min term | designation    |

|-----|---|---|----------|----------------|

| 0   | 0 | 0 | A'B'C'   | m <sub>0</sub> |

| 0   | 0 | 1 | A'B'C    | $\mathbf{m}_1$ |

| 0   | 1 | 0 | A'BC'    | m <sub>2</sub> |

| 0   | 1 | 1 | A'BC     | $m_3$          |

| _ 1 | 0 | 0 | AB'C'    | m <sub>4</sub> |

| 1   | 0 | 1 | AB'C     | m <sub>5</sub> |

| 1   | 1 | 0 | ABC'     | m <sub>6</sub> |

| 1   | 1 | 1 | ABC      | m <sub>7</sub> |

#### STANDARD FORM AND CANONICAL FORM

#### **STANDARD FORMS:**

- In standard form the terms that form the function may contain one, two or any number of literals/variables. There are two types of standard forms.

- Sum of Product (SOP)

- Product of Sum (POS)

#### Sum of Product (SOP)

- SOP is a Boolean expression containing terms with AND logic of 1 or more literals.

- E.g. F=XYZ+X'YZ+X'Y'Z

#### Product of Sum(POS)

- POS is a Boolean expression containing terms with OR logic of 1 or more literals.

- E.g. F=(X+Y+Z)(X'+Y+Z)(X'+Y'+Z)

- K-MAP is regarded as a diagrammatic or pictorial form of a truth table.

- The map is a diagram made up of squares.

- Each square represents one min/ max term.

- The MAP represents a visual diagram of all possible ways of function, may ne expressed in a standard form.

#### **Basic K-MAP**

| В    |   | В'   | В   |

|------|---|------|-----|

| A    |   | 0    | 1   |

| A' 0 |   | A'B' | A'B |

| A    | 1 | AB'  | AB  |

Fig: Two variable K-MAP

#### Three variable K-MAP

- There are 8 min terms for 3 binary variables.

- A MAP consists of 8 squares.

- The min terms are arranged not in a binary sequence but in sequence similar to gray code.

- The characteristics of the sequence is that only one bit is changes from one sequence to another.

| BC |   | B'C'           | В'С            | BC             | BC'            |

|----|---|----------------|----------------|----------------|----------------|

| A  |   | 00             | 01             | 11             | 10             |

| A' | 0 | $m_0$          | m <sub>1</sub> | m <sub>3</sub> | m <sub>2</sub> |

| A  | 1 | m <sub>4</sub> | m <sub>5</sub> | m <sub>7</sub> | m <sub>6</sub> |

Fig: Three variable K-MAP

#### Four variable K-MAP

- There are 16 min terms for 4 binary variables.

- A MAP consists of 16 squares.

| CI. | 100  | 10  |      |   |

|-----|------|-----|------|---|

| Sim | nlit | ıca | fion | В |

|     | 7444 | Ten | CLUI | 2 |

- One square box represents one min term giving a term of four literals.

- Two adjacent square box represents a term of three literals

- Four adjacent square box represents a term of two literals.

| /0   | C <b>D</b> | C'D'            | C'D             | CD              | CD'             |

|------|------------|-----------------|-----------------|-----------------|-----------------|

| A    | В          | 00              | 01              | 11              | 10              |

| A'B' | 00         | m <sub>0</sub>  | m <sub>1</sub>  | m <sub>3</sub>  | m <sub>2</sub>  |

| A'B  | 01         | m <sub>4</sub>  | m <sub>5</sub>  | $\mathbf{m}_7$  | m <sub>6</sub>  |

| AB   | 11         | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> |

| AB'  | 10         | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> |

Fig: Four variable K-MAP

- Eight square box represents one min term giving a term of one literals.

- Sixteen adjacent square box represents a function 1

- Zero square box represents a function 0.

#### **DON'T CARE CONDITION:**

- There are some condition of inputs for which output is not specified and such output does not affect the whole system, which are known as Don't Care condition.

- The Don't care min terms are denoted by 'X' sign.

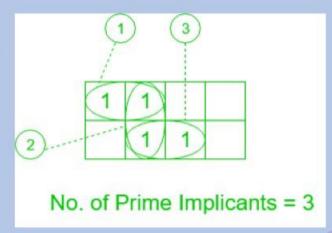

#### **IMPLICANTS IN K-MAP**

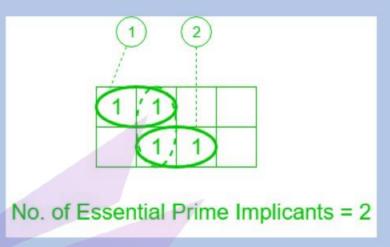

#### Prime Implicants

A group of square or rectangle made up of bunch of adjacent minterms which is allowed by definition of K-Map are called prime implicants(PI) i.e. all possible groups formed in K-Map.

#### Essential Prime Implicants

These are those sub cubes (groups) which cover at least one minterm that can't be covered by any other

prime implicant. Essential prime implicants(EPI) are those prime implicants which always appear in final

solution.

E.G.

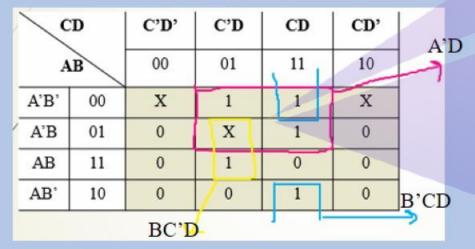

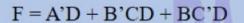

#### **K-MAP EXAMPLE:**

Simplify using K-MAP and design a logic circuit.

$$F(A,B,C,D) = \sum (1,3,7,11,13)$$

and the don't care condition  $D(A,B,C,D) = \sum (0,2,5)$

Fig: Combinational Design

- 1 Algebra of logic is termed as \_\_\_\_\_

- a) Numerical logic

- Boolean algebra

- c) Arithmetic logic

- d) Boolean number

- 2 Boolean algebra can be used \_\_\_\_\_

- For designing of the digital computers

- b) In building logic symbols

- c) Circuit theory

- d) Building algebraic functions

- **3** F(X,Y,Z,M) = X`Y`Z`M`. The degree of the function is \_\_\_\_\_

- a) 2

- b) 5

- 4

- d) 1

- 4 A \_\_\_\_\_ value is represented by a Boolean expression

- a) Positive

- b) Recursive

- c) Negative

- Boolean

- 5 What are the canonical forms of Boolean Expressions?

- a) OR and XOR

- b) NOR and XNOR

- MAX and MIN

- d) SOM and POM

- 6 . The \_\_\_\_\_ of all the variables in direct or complemented from is a maxterm.

- addition

- b) product

- c) moduler

- d) subtraction

- 7 Which of the following is/are the universal logic gates?

- a) OR and NOR

- b) AND

- NAND and NOR

- d) NOT

- 8 The logic gate that provides high output for same inputs \_\_\_\_\_

- a) NOT

- X-NOR

- c) AND

- d) XOR

- 9 Which of the following bits is the negation of the bits "010110"?

- a) 111001

- b) 001001

- 101001

- d) 111111

- 10 How many bits string of length 4 are possible such that they contain 2 ones and 2 zeroes?

- a) 4

- b) 2

- c) 5

- 6

- 11 If a bit string contains {0, 1} only, having length 5 has no more than 2 ones in it. Then how many such bit strings are possible?

- a) 14

- b) 12

- c) 15

- 16

- 12 . If A is "001100" and B is "010101" then what is the value of A (Ex-or) B?

- a) 000000

- b) 111111

- c) 001101

- 011001

- 13 Which of the following option is suitable, if A is "10110110", B is "11100000" and C

- is"10100000"?

- a) C=A or B

- b) C=~A

- c) C=~B

- C=A and B

- 14 . The Ex-nor of this string "01010101" with "11111111" is?

- a) 10101010

- b) 00110100

- 01010101

- d) 10101001

- What is the one's complement of this string "01010100"?

- a) 10101010

- b) 00110101

- 10101011

- d) 10101001

- 18 What is the 2's complement of this string "01010100"?

- a) 10101010

- b) 00110100

- 10101100

- d) 10101001

The minimum number of NAND gates required to reduce the expression ((A + B)C) D is:

- Let A: "010101", B=?, If { A (Ex-or) B } is a resultant string of all ones then which of the following statement regarding B is correct?

- a) B is negation of A

- b) B is 101010

- c) {A (and) B} is a resultant string having all zeroes

All of the mentioned

- 21 The terms in SOP are called \_\_\_\_\_

- a) max terms

- min terms

- c) mid terms

- d) sum terms

- Which of the following is an incorrect SOP expression?

- a) x+x.y

- (x+y)(x+z)

- c) x

- d) x+y

- 5. The NOR gate output will be high if the two inputs are \_\_\_\_\_ 00 b) 01

- c) 10

- d) 11

- 24. LSI stands for \_\_\_\_\_

- Large Scale Integration

- b) Large System Integration

- c) Large Symbolic Instruction

- d) Large Symbolic Integration

- 25

- 4. The corresponding min term when x=0, y=0 and z=1.

- a) x.y.z'

- b) X'+Y'+Z

- c) X+Y+Z'

- x'.y'.z

- 26 . Which operation is shown in the following expression: (X+Y').(X+Z).(Z'+Y')

- a) NOR

- b) ExOR

- c) SOP

- POS

- 27 The number of min terms for an expression comprising of 3 variables?

- 8

- b) 3

- c)0

- d) 1

- The number of cells in a K-map with n-variables.

- a) 2n

- b) n<sup>2</sup>

- 2<sup>n</sup>

- d) n

- 29 The output of AND gates in the SOP expression is connected using the \_\_\_\_\_ gate.

- a) XOR

- b) NOR

- c) AND

- OR

- 30 . The expression A+BC is the reduced form of \_\_\_\_\_

- a) AB+BC

- (A+B)(A+C)

- c) (A+C)B

- d) (A+B)C

- A Karnaugh map (K-map) is an abstract form of \_\_\_\_\_\_ diagram organized as a matrix of squares.

- Venn Diagram

- b) Cycle Diagram

- c) Block diagram

- d) Triangular Diagram

- 32 Each product term of a group, w'.x.y' and w.y, represents the \_\_\_\_\_\_ in that group.

- a) Input

- b) POS

- Sum-of-Minterms

- d) Sum of Maxterms

- 33 There are \_\_\_\_ cells in a 4-variable K-map.

- a) 12

- 16

- c) 18

- d) 8

- The prime implicant which has at least one element that is not present in any other

- implicant is known as \_\_\_\_\_

- Essential Prime Implicant

- b) Implicant

- c) Complement

- d) Prime Complement

- 35 It should be kept in mind that don't care terms should be used along with the terms that

- are present in \_\_\_\_\_

- Minterms

- b) Expressions

- c) K-Map

- d) Latches

- 36 Product-of-Sums expressions can be implemented using \_\_\_\_\_

- a) 2-level OR-AND logic circuits

- b) 2-level NOR logic circuits

- c) 2-level XOR logic circuits

- Both 2-level OR-AND and NOR logic circuits

- Each group of adjacent Minterms (group size in powers of twos) corresponds to a possible product term of the given \_\_\_\_\_

- Function

- b) Value

- c) Set

- d) Word

- 38 Don't care conditions can be used for simplifying Boolean expressions in \_\_\_\_\_

- a) Registers

- b) Terms

- K-maps

- d) Latches

PANA ACADEMY

39

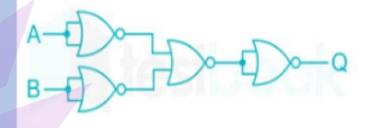

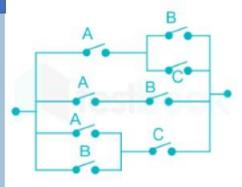

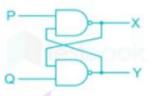

From the given arrangement, find Q.

$$\overline{A} + \overline{B}$$

4. More than one of the above

The following truth-table belongs to which one of the four gates-

40

| Α | В | × |

|---|---|---|

| 1 | 1 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 0 | 0 | 1 |

1. OR

NOR

- 3. XOR

- 4. More than one of the above

PANA ACADEMY

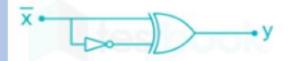

41 The output of the logic gate in figure is

A F

- 1. 0

- 2. 1

4. A

42

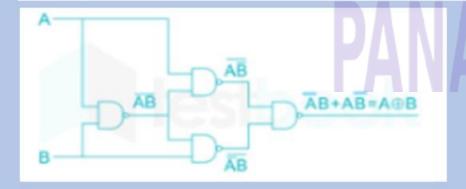

The output of logic circuit given below represents \_\_\_\_ gate.

- 1. OR

- 2. NOR

3. AND

The minimum number of 2-input NAND gates required to implement a 2-input XOR gate is

2. 5

3. 6

4. 7

44

The output Y of the logic circuit given below is:-

2. 1

3. X

4. X

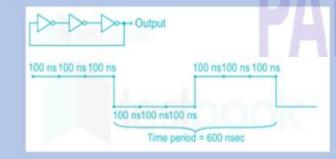

4.5 What will be the fundamental frequency for the following circuit if each inverter delay is 100 nsec?

1. 1 GHz

2. 0.5 GHz

3. 3.34 MHz

1.67 MHz

46

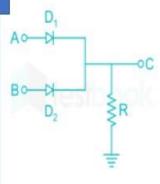

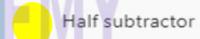

Which of the following logical operations could be computed by the given network?

1. C = AB

3.

$$C = \overline{AB}$$

4.

$$C = \overline{A + B}$$

4.7 Boolean expression AB + AC̄ + BC simplifies to

48 How many AND and OR gates are required to realise Y = AB + BC + CD?

2.

$$AB + A\overline{C} + B$$

3.

$$AB + A\bar{C}$$

4. AB + BC

2. 2, 1

1. 2, 3

3,

4, 2, 2

he following hexadecimal number (1E.43)16 is equivalent to

a. (36.506)<sub>8</sub>

(36.206)8

c. (35.506)<sub>8</sub>

d. (35.206)<sub>8</sub>

50 How many bits are needed to store one BCD digit?

a. 2 bits

4 bits

c. 3 bits

d. 1 bit

# PANA ACADEMY

- The code where all successive numbers differ from their preceding number by single bit is \_\_\_\_\_\_

- a) Alphanumeric Code

- b) BCD

- c) Excess 3

- Gray

- 52 . How many AND gates are required to realize Y = CD + EF + G?

- a) 4

- b) 5

- c) 3

- $\bigcirc$ 2

PANA ACADEMY

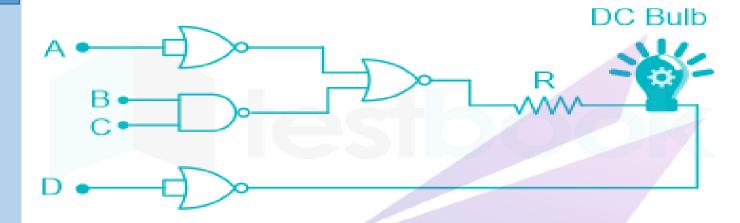

Following gates section is connected in a complete suitable circuit.

For which of the following combination, bulb will glow (ON):

4.

$$A = 1$$

,  $B = 1$ ,  $C = 1$ ,  $D = 0$

# THANK YOU

PANA ACADEMY

# 2. Digital Logic and Microprocessor

PANA ACADEMY

Er. Pralhad Chapagain

# Syllabus

- 2.1 Digital logic: Number Systems, Logic Levels, Logic Gates, Boolean algebra, Sum-of-Products Method, Product-of-Sums Method, Truth Table to Karnaugh Map. (AExE0201)

- 2.2 Combinational and arithmetic circuits: Multiplexetures, Demultiplexetures, Decoder, Encoder, Binary Addition, Binary Subtraction, operation on Unsigned and Signed Binary Numbers. (AExE0202)

- 2.3 Sequential logic circuit: RS Flip-Flops, Gated Flip-Flops, Edge Triggered Flip-Flops, Mater- Slave Flip-Flops. Types of Registers, Applications of Shift Registers, Asynchronous Counters, Synchronous Counters.

(AExE0203)

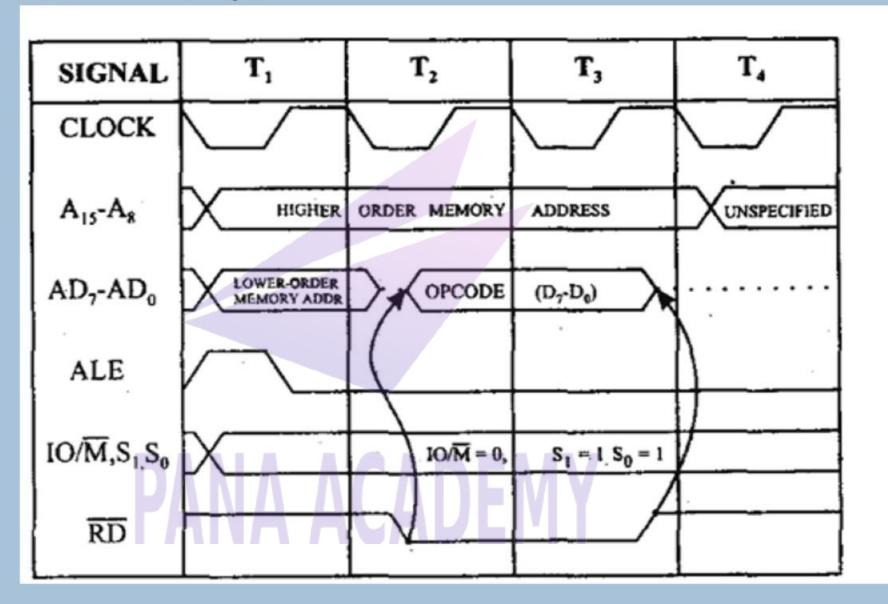

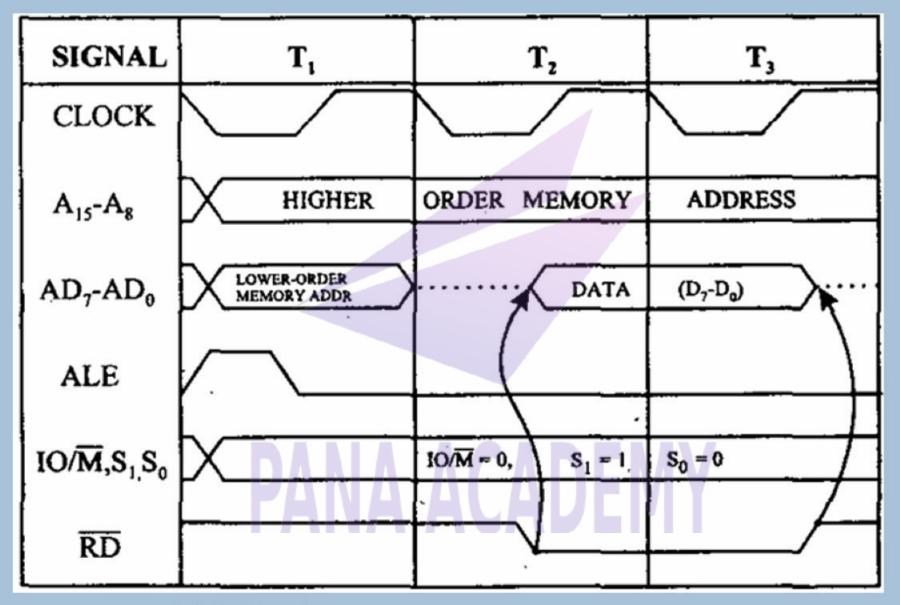

- 2.4 Microprocessor: Internal Architecture and Features of microprocessor, Assembly Language Programming.

(AExE0204)

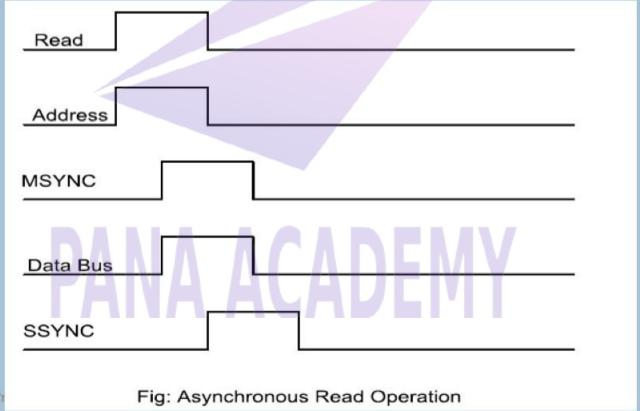

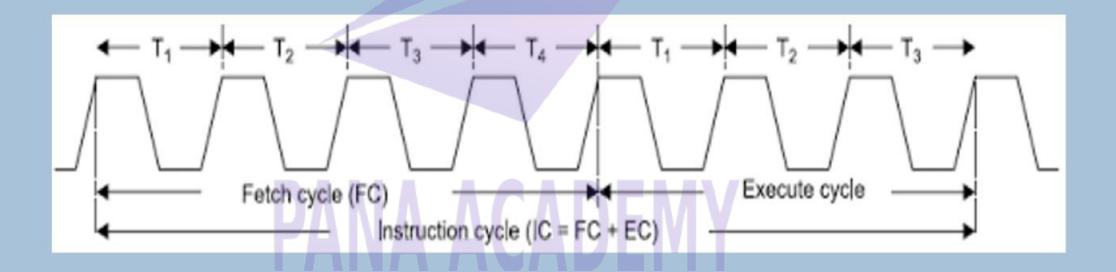

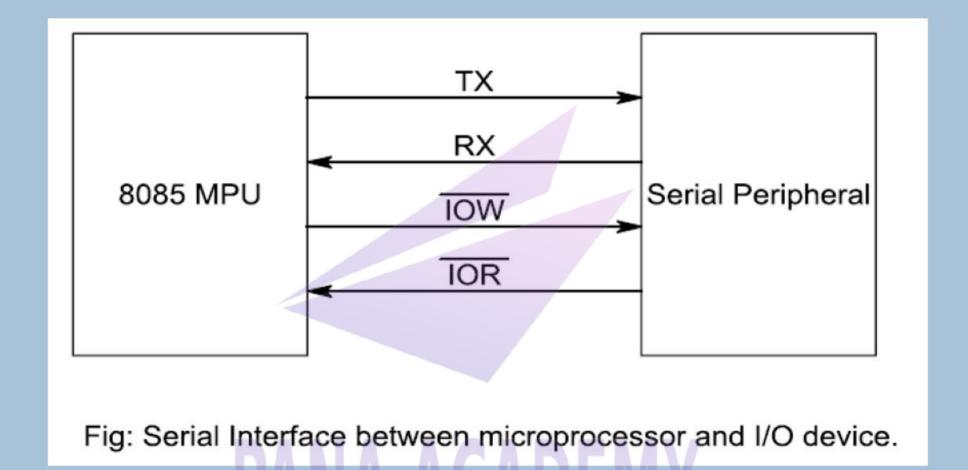

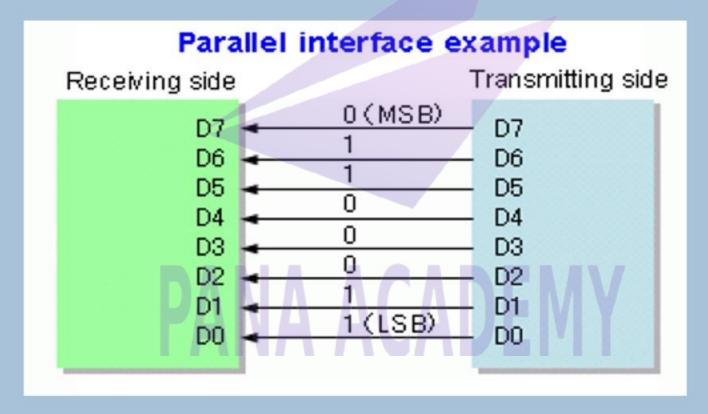

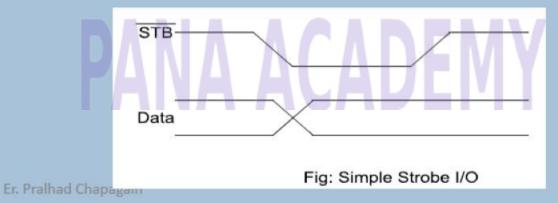

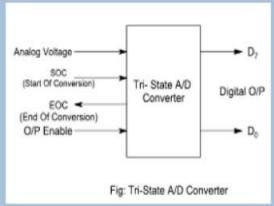

- 2.5 Microprocessor system: Memory Device Classification and Hierarchy, Interfacing I/O and Memory Parallel Interface. Introduction to Programmable Peripheral Interface (PPI), Serial Interface, Synchronous and Asynchronous Transmission, Serial Interface Standards. Introduction to Direct Memory Access (DMA) and DMA Controllers.

(AEXE0205)

- 2.6 Interrupt operations: Interrupt, Interrupt Service Routine, and Interrupt Processing. (AExE0206)

2.2 Combinational and arithmetic circuits: Multiplexetures, Demultiplexetures, Decoder, Encoder, Binary Addition, Binary Subtraction, operation on Unsigned and Signed Binary Numbers. (AExE0202)

# PANA ACADEMY

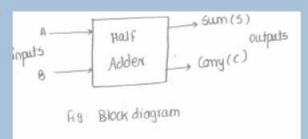

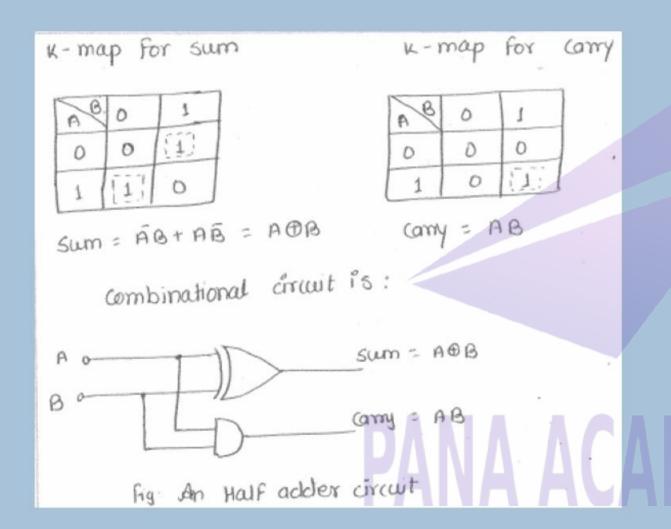

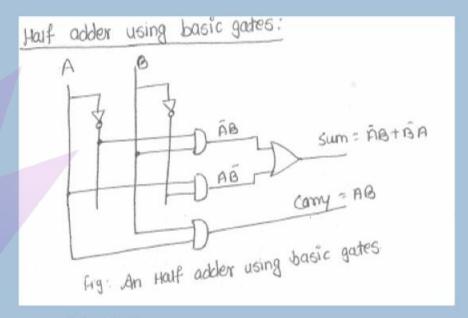

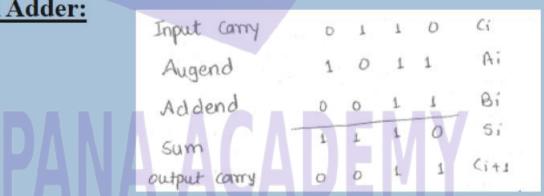

#### **ADDER - HALF**

- Binary adders nay be of two types:

- Half Adder

- Full Adder

#### Half Adder:

- Half adder is a combinational logic circuit with two inputs and two outputs.

- It is the basic building block for

addition of two single bit numbers

This circuit has two outputs namely,

Sum and Carry.

Truth table:

| Inj | outs | Outputs |       |  |

|-----|------|---------|-------|--|

| A   | В    | Sum     | Carry |  |

| 0   | 0    | 0       | 0     |  |

| 0   | 1    | 1       | 0     |  |

| 1   | 0    | 1       | 0     |  |

| 1   | 1    | 0       | 1     |  |

#### **ADDER - HALF**

- · Limitations:

- The addition of three bits is not possible

to perform by using an half adder circuit.

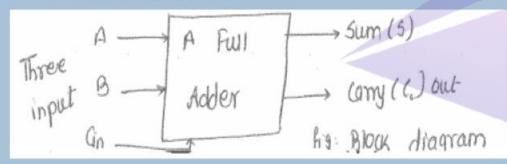

#### **ADDER - FULL**

#### Full Adder:

- To overcome the drawback of an half adder circuit, a 3-single bit adder circuit called full adder is developed.

- Basically, a full adder is a three input and two output combinational circuit.

Application: A full adder acts as the basic building block of the 4 bit/ 8 bit binary/ BCD adder Ics such as 7483.

#### Truth table:

|   | Inputs |          | O   | Outputs                 |  |  |

|---|--------|----------|-----|-------------------------|--|--|

| A | В      | $C_{in}$ | Sum | Carry (C <sub>o</sub> ) |  |  |

| 0 | 0      | 0        | 0   | 0                       |  |  |

| 0 | 0      | 1        | 1   | 0                       |  |  |

| 0 | 1      | 0        | 1   | 0                       |  |  |

| 0 | 1      | 1        | 0   | 1                       |  |  |

| 1 | 0      | 0        | 1   | 0                       |  |  |

| 1 | 0      | 1        | 0   | 1                       |  |  |

| 1 | 1      | 0        | 0   | 1                       |  |  |

| 1 | 1      | 1        | 1   | 1                       |  |  |

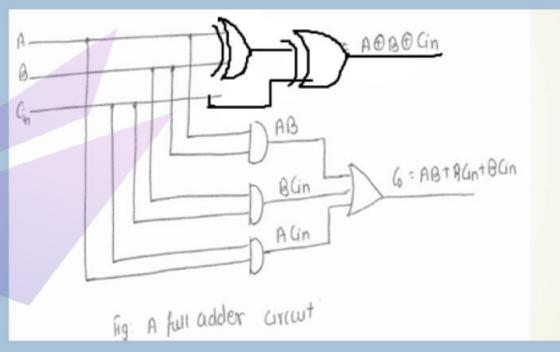

#### **ADDER - FULL**

#### 4-map for sum (5)

| AC | 00 | 0 1 | 1 1 | 10   |

|----|----|-----|-----|------|

| 0  | 0  | [1] | 0   | 12.7 |

| 1  | 11 | 0   | [1] | 0    |

S = A'B' Cin + A'B Cin + AB' Cin +

ABCin

= ABBBGn

K-map for carry out (6)

| Bun | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

| 0   | 0  | 0  | 11 | 0  |

| 1   | 0  | 11 | 13 | 17 |

Co = AGn + BGin + AB

# CADEMY

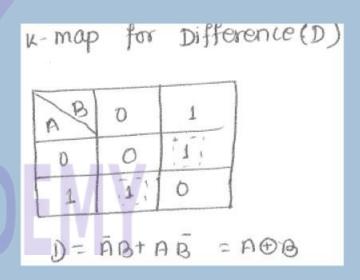

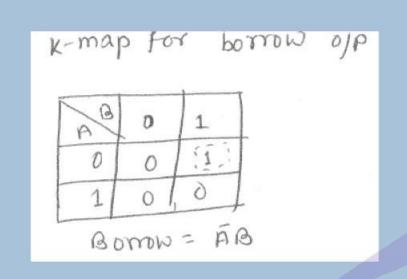

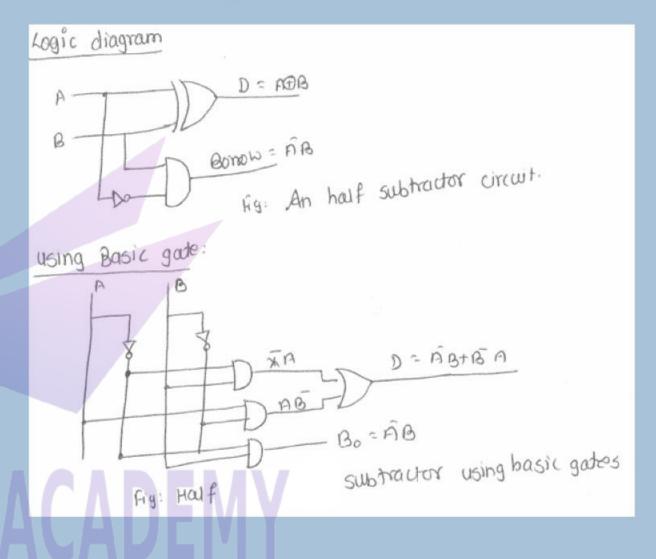

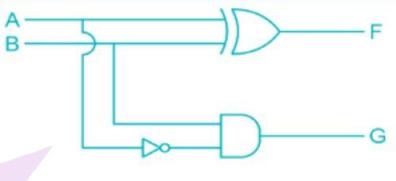

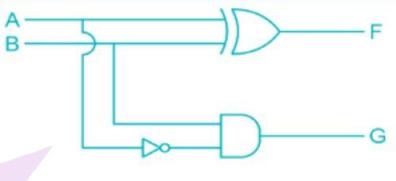

#### **SUBTRACTOR - HALF**

- Binary Subtractor nay be of two types:

- Half Subtractor

- Full Subtractor

#### **Half Subtractor:**

- Half subtractor may be defined as combinational circuit with two inputs and two outputs (i.e. difference and borrow)

- In subtraction (A-B), A is called minuend bit and B is called as Subtrahend bit.

Truth table:

| Inp | uts | Outputs          |                          |  |  |

|-----|-----|------------------|--------------------------|--|--|

| A   | В   | Difference (A-B) | Borrow (B <sub>o</sub> ) |  |  |

| 0   | 0   | 0                | 0                        |  |  |

| 0   | 1   | 1                | 1                        |  |  |

| 1   | 0   | 1                | 0                        |  |  |

| 1   | 1   | 0                | 0                        |  |  |

### **SUBTRACTOR - HALF**

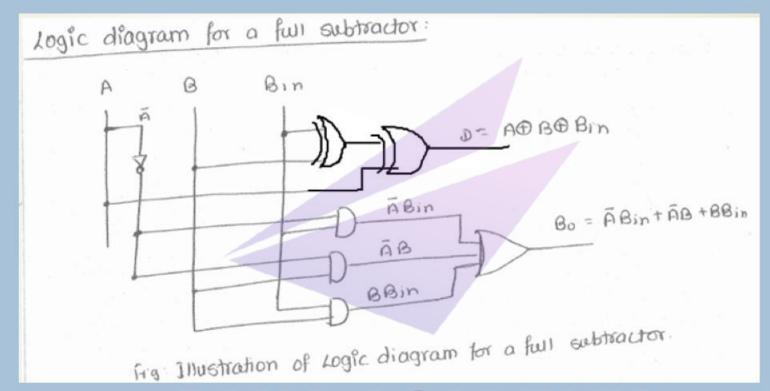

#### **SUBTRACTOR - FULL**

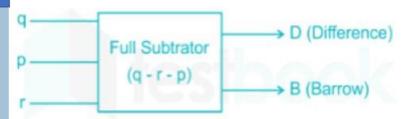

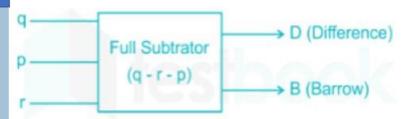

#### **Full Subtractor:**

• A Full Subtractor is a combinational circuit with three inputs A, B, B<sub>in</sub> and two outputs D (Difference) and Borrow (B<sub>o</sub>)

• Here A is the minuend, B is the subtrahend,  $B_{in}$  is the borrow produced by the previous stage,

D is the difference output and  $B_o$  is the borrow output.

Truth table:

| I | Inputs |     | Outputs                           |                          |  |

|---|--------|-----|-----------------------------------|--------------------------|--|

| A | В      | Bin | Difference (A-B-B <sub>in</sub> ) | Borrow (B <sub>o</sub> ) |  |

| 0 | 0      | 0   | 0                                 | 0                        |  |

| 0 | 0      | 1   | 1                                 | 1                        |  |

| 0 | 1      | 0   | 1                                 | 1                        |  |

| 0 | 1      | 1   | 0                                 | 1                        |  |

| 1 | 0      | 0   | 1                                 | 0                        |  |

| 1 | 0      | 1   | 0                                 | 0                        |  |

| 1 | 1      | 0   | 0                                 | 0                        |  |

| 1 | 1      | 1   | 1                                 | 1                        |  |

#### **SUBTRACTOR - FULL**

K-map

For difference output

| BBin | 00 | 101 | 1 1 | 10 |

|------|----|-----|-----|----|

| 0    | 0  | [1] | 0   | 11 |

| 1    | 11 | 0   | [1] | 0  |

D = ABBin + ABBin + ABBin + ABBin

= ADBOBin

| Fox | Borrow | autput |  |

|-----|--------|--------|--|

|     |        |        |  |

| 8Bin | 00 | 01 | 11  | 10 |

|------|----|----|-----|----|

| 0    | 0  | 11 | 11  | 1) |

| 1    | 0  | 0  | 11: | 0  |

#### **SUBTRACTOR - FULL**

# PANA ACADEMY

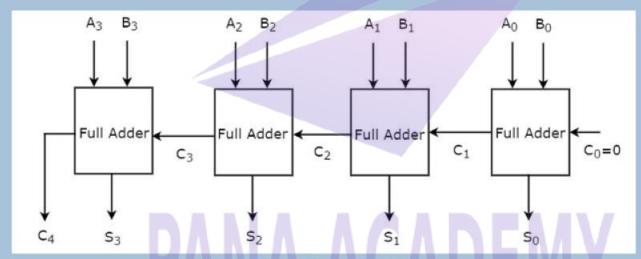

#### **BINARY PARALLEL ADDER**

- A full adder is capable of adding only two single digit binary numbers along with a carry input.

- But, in practice, we need to add binary numbers which are much longer than just one bit.

- To add two n- bit binary numbers, we need to use the n-bit parallel adder.

- It makes use of a number of full adders in cascade.

- The carry output of the previous full adder is connected to the carry input of the next full adder.

#### A 4-bit Binary Parallel Adder:

#### **BINARY PARALLEL ADDER**

- A binary parallel adder is a digital function that produces the arithmetic sum of two binary numbers in parallel.

- It consists of full-adder connected in cascade, with the output carry from one full adder connected to the input carry of the next full-adder.

Fig: 4-bit Binary Parallel adder

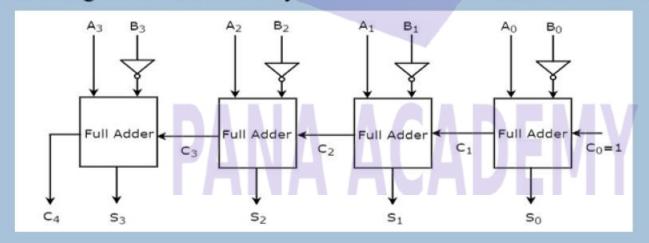

#### 4-BIT BINARY PARALLEL SUBTRACTOR

- The 4-bit binary subtractor produces the subtraction of two 4-bit numbers.

- Let the 4 bit binary numbers,  $A=A_3A_2A_1A_0$  and  $B=B_3B_2B_1B_0$ .

- Internally, the operation of 4-bit Binary subtractor is similar to that of 4-bit Binary adder.

- If the normal bits of binary number A, complemented bits of binary number B and initial carry borrow, C<sub>in</sub> as one are applied to 4-bit Binary adder, then it becomes 4-bit Binary subtractor.

- The block diagram of 4-bit binary subtractor is shown in the following figure.

Note: A-B = A + B' + 1

#### 4-BIT BINARY PARALLEL SUBTRACTOR

- This 4-bit binary subtractor produces an output, which is having at most 5 bits.

- If Binary number A is greater than Binary number B, then MSB of the output is zero and the remaining bits hold the magnitude of A-B.

- If Binary number A is less than Binary number B, then MSB of the output is one. So, take the 2's complement of output in order to get the magnitude of A-B

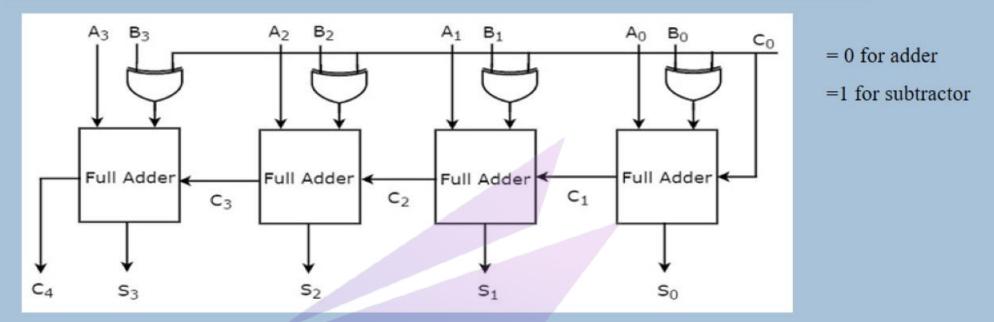

#### 4-BIT BINARY PARALLEL ADDER/SUBTRACTOR

- The circuit, which can be used to perform either addition or subtraction of two binary numbers at any time is known as Binary Adder / subtractor.

- Both, Binary adder and Binary subtractor contain a set of Full adders, which are cascaded.

- The input bits of binary number A are directly applied in both Binary adder and Binary subtractor.

- The input bits of binary number B are directly applied to Full adders in Binary adder, whereas the complemented bits of binary number B are applied to Full adders in Binary subtractor.

- The initial carry, C<sub>0</sub> = 0 is applied in 4-bit Binary adder, whereas the initial carry borrow, C<sub>0</sub> = 1

is applied in 4-bit Binary subtractor.

- We know that a 2-input Ex-OR gate produces an output, which is same as that of first input when other input is zero. Similarly, it produces an output, which is complement of first input when other input is one.

#### 4-BIT BINARY PARALLEL ADDER/SUBTRACTOR

- If initial carry,  $C_0$  is zero, then each full adder gets the normal bits of binary numbers A & B. So, the 4-bit binary adder / subtractor produces an output, which is the addition of two binary numbers A & B.

- If initial borrow, C<sub>0</sub> is one, then each full adder gets the normal bits of binary number A & complemented bits of binary number B. So, the 4-bit binary adder / subtractor produces an output, which is the subtraction of two binary numbers A & B.

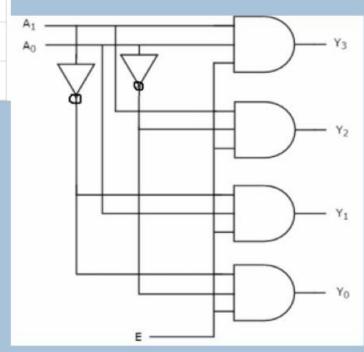

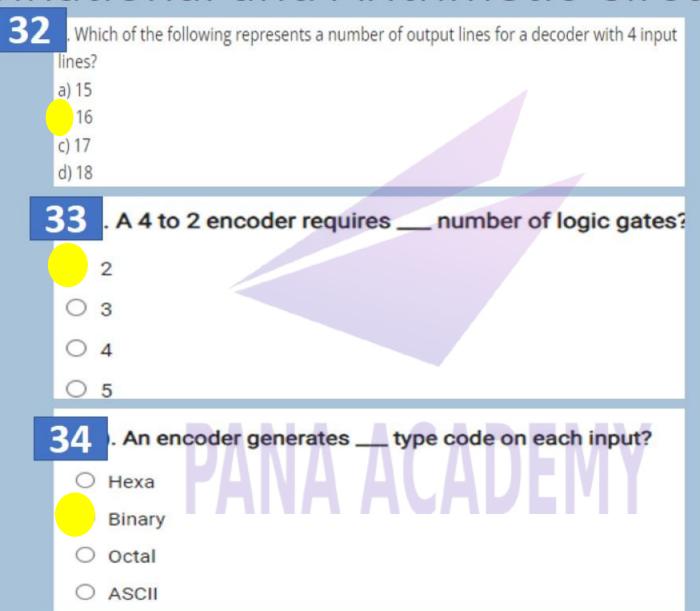

#### **DECODERS**

19

- Decoder is a combinational circuit that has 'n' input lines and maximum of 2<sup>n</sup> output lines.

- One of these outputs will be active High based on the combination of inputs present, when the decoder is enabled.

- That means decoder detects a particular code. The outputs of the decoder are nothing but the min terms of 'n' input variables lines, when it is enabled.

#### 2 to 4 Decoder

Let 2 to 4 Decoder has two inputs A1 & A0 and four outputs Y3, Y2, Y1 & Y0. The block diagram of 2 to 4 decoder is shown in the following figure.

#### **DECODERS**

20

One of these four outputs will be '1' for each combination of inputs when enable, E is '1'. The Truth table of 2 to 4 decoder is shown below.

| Enable | Inp            | uts   | Outputs               |                |                |                       |

|--------|----------------|-------|-----------------------|----------------|----------------|-----------------------|

| E      | A <sub>1</sub> | $A_0$ | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | <b>Y</b> <sub>0</sub> |

| 0      | X              | X     | 0                     | 0              | 0              | 0                     |

| 1      | 0              | 0     | 0                     | 0              | 0              | 1                     |

| 1      | 0              | 1     | 0                     | 0              | 1              | 0                     |

| 1      | 1              | 0     | 0                     | 1              | 0              | 0                     |

| 1      | 1              | 1     | 1                     | 0              | 0              | 0                     |

From Truth table, we can write the Boolean functions for each output as

$$Y_3 = E. A_1. A_0$$

$Y_2 = E.\,A_1.\,A_0{}'$   $Y_1 = E.\,A_1{}'.\,A_0$

$$Y_0 = E. A_1'. A_0'$$

Er. Pralhad Chapagain

#### **DECODERS**

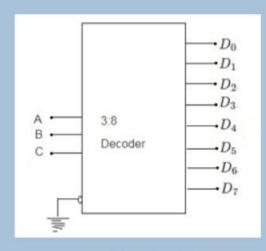

#### 21 3 X 8 DECODER:

#### Truth Table

| Α | В | С | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

|---|---|---|----|----|----|----|----|----|----|----|

| 0 | 0 | 0 | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0 | 0 | 1 | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0 | 1 | 0 | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 0 | 1 | 1 | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 1 | 0 | 0 | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1 | 0 | 1 | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 1 | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 1 | 1 | 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

#### Function

$$D_0 = \overline{A}\overline{B}\overline{C}, \quad D_1 = \overline{A}\overline{B}C, \quad D_2 = \overline{A}B\overline{C},$$

$D_3 = \overline{A}BC, \quad D_4 = A\overline{B}\overline{C}, \quad D_5 = A\overline{B}C,$

$D_6 = AB\overline{C}, \quad D_7 = ABC$

#### Block Diagram

Logic Diagram

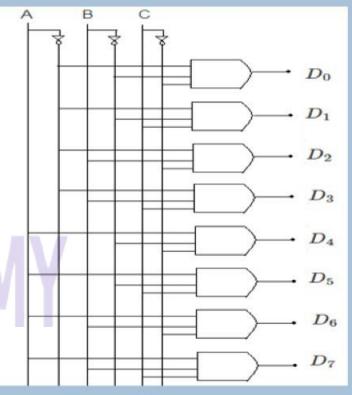

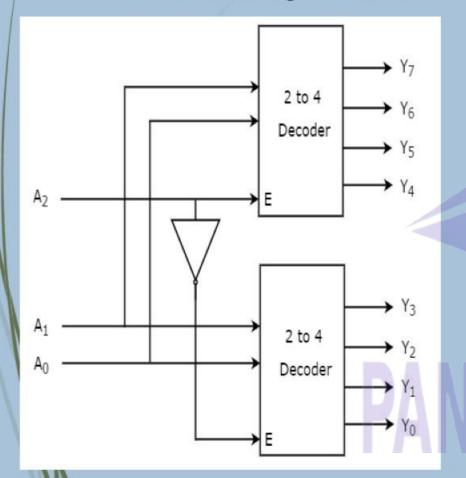

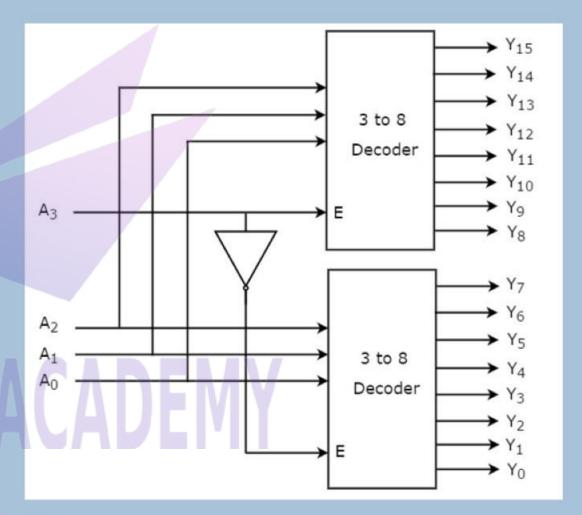

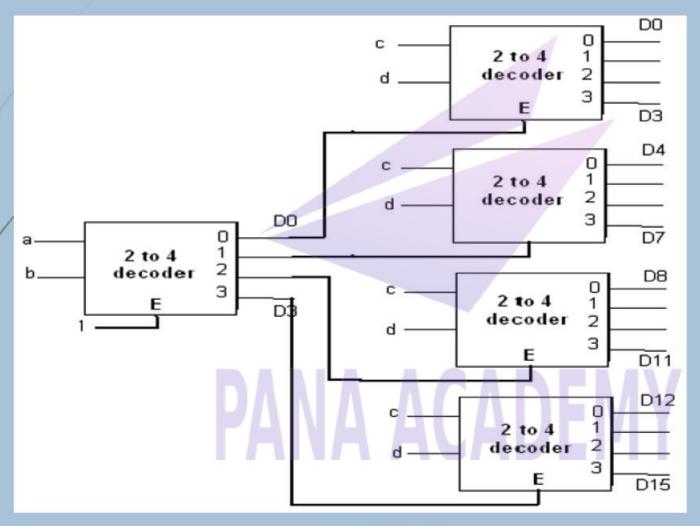

#### IMPLEMENTATION OF HIGHER ORDER DECODERS

22

3 to 8 decoder using 2 to 4 decoder

4 to 16 decoder using 3 to 8 decoder

Er. Pralhad Chapagain

4 to 16 decoder using 2 to 4 decoder

Er. Pralhad Chapagain

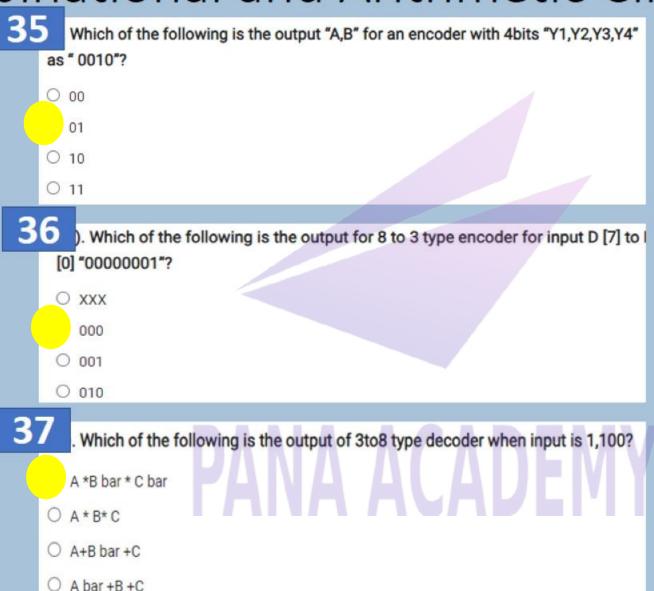

#### **ENCODERS**

24

- An Encoder is a combinational circuit that performs the reverse operation of Decoder.

- It has maximum of 2<sup>n</sup> input lines and 'n' output lines.

- It will produce a binary code equivalent to the input, which is active High.

- Therefore, the encoder encodes 2<sup>n</sup> input lines with 'n' bits. It is optional to represent the enable signal in encoders.

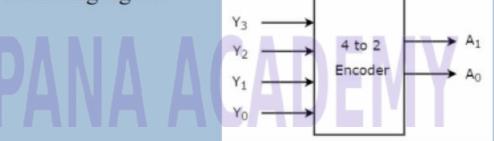

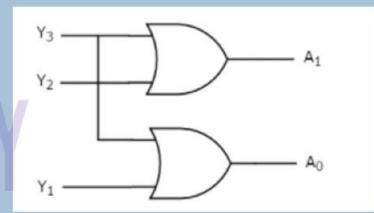

#### 4 to 2 Encoder

Let 4 to 2 Encoder has four inputs  $Y_3$ ,  $Y_2$ ,  $Y_1$  &  $Y_0$  and two outputs  $A_1$  &  $A_0$ . The block diagram of 4 to 2 Encoder is shown in the following figure.

## **ENCODERS**

25

At any time, only one of these 4 inputs can be '1' in order to get the respective binary code at the output. The Truth table of 4 to 2 encoder is shown below.

|                | Inp            | Outp           | outs                  |                |                |

|----------------|----------------|----------------|-----------------------|----------------|----------------|

| Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | <b>Y</b> <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> |

| 0              | 0              | 0              | 1                     | 0              | 0              |

| 0              | 0              | 1              | 0                     | 0              | 1              |

| 0              | 1              | 0              | 0                     | 1              | 0              |

| 1              | 0              | 0              | 0                     | 1              | 1              |

From Truth table, we can write the Boolean functions for each output as

$$A_1=Y_3+Y_2$$

$A_0=Y_3+Y_1$

#### Logic Diagram

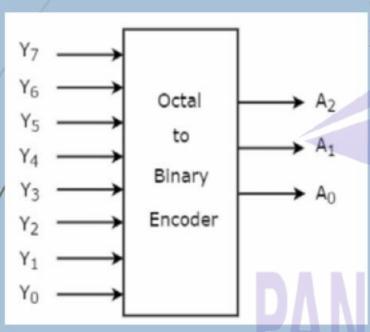

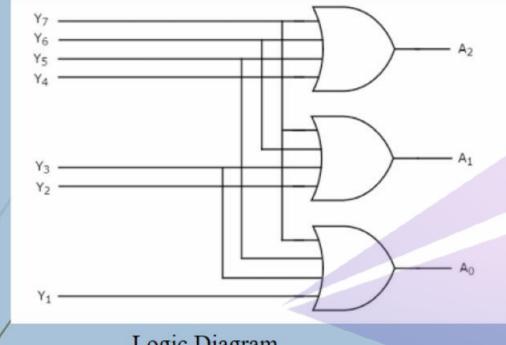

## **ENCODERS – OCTAL TO BINARY ENCODER**

26

Octal to binary Encoder has eight inputs, Y7 to Y0 and three outputs A2, A1 & A0.

Octal to binary encoder is nothing but 8 to 3 encoder. The block diagram of octal to binary Encoder is

shown in the following figure

Truth Table and Function

|                | Inputs         |                |                |                |                |                |                | Outputs        |                |   |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|

| Y <sub>7</sub> | Y <sub>6</sub> | Y <sub>5</sub> | Y <sub>4</sub> | Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> | A <sub>2</sub> | A <sub>1</sub> | A |

| 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0 |

| 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 1 |

| 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 1              | 0 |

| 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 1              | 1 |

| 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 1              | 0              | 0 |

| 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 1 |

| 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1              | 0 |

| 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1              | 1 |

From Truth table, we can write the Boolean functions for each output as

$$A_2 = Y_7 + Y_6 + Y_5 + Y_4$$

$$A_1 = Y_7 + Y_6 + Y_3 + Y_2$$

$$A_0 = Y_7 + Y_5 + Y_3 + Y_1$$

Er. Pralhad Chapagain

Logic Diagram

#### **Drawbacks of Encoder**

- There is an ambiguity, when all outputs of encoder are equal to zero

- If more than one input is active High, then the encoder produces an output, which may not be the correct code.

## **ENCODERS – PRIORITY ENCODER**

28

We considered one more output, V in order to know, whether the code available at outputs is valid or not.

- If at least one input of the encoder is '1', then the code available at outputs is a valid one. In this case, the output,

V will be equal to 1.

- ► If all the inputs of encoder are '0', then the code available at outputs is not a valid one. In this case, the output, V will be equal to 0.

Truth Table

|                       | Inputs         |                |                       |                | Outputs               |   |  |

|-----------------------|----------------|----------------|-----------------------|----------------|-----------------------|---|--|

| <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | <b>Y</b> <sub>0</sub> | A <sub>1</sub> | <b>A</b> <sub>0</sub> | V |  |

| 0                     | 0              | 0              | 0                     | 0              | 0                     | 0 |  |

| 0                     | 0              | 0              | 1                     | 0              | 0                     | 1 |  |

| 0                     | 0              |                | X                     | 0              | 1                     | 1 |  |

| 0                     | 1              | ×              | х                     | AU             | 0                     | 1 |  |

| 1                     | x              | X              | х                     | 1              | 1                     | 1 |  |

Er. Pralhad Chapagain

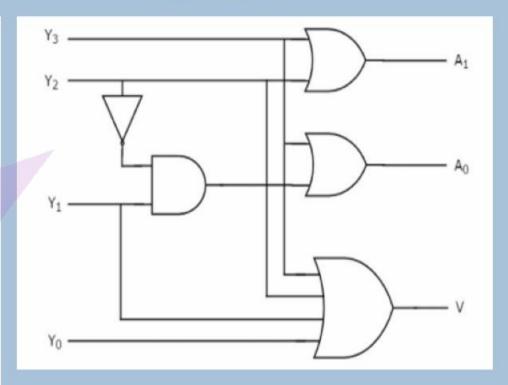

## **ENCODERS – PRIORITY ENCODER**

29

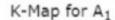

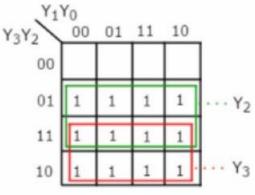

#### K-MAP and Function

K-Map for A<sub>0</sub>

The simplified Boolean functions are

$$A_1 = Y_3 + Y_2$$

$$A_0 = Y_3 + Y_2' Y_1$$

Similarly, we will get the Boolean function of output, V as

$$V = Y_3 + Y_2 + Y_1 + Y_0$$

#### Logic Diagram

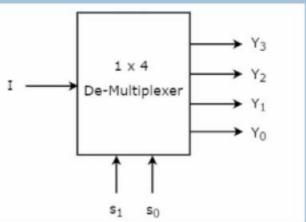

## **DEMULTIPLEXERS (DEMUX)**

30

- A demultiplexer (or demux) is a device that takes a single input line and routes it to one of several digital output lines.

- A demultiplexer of 2<sup>n</sup> outputs has n select lines, which are used to select which output line to send the input.

- A demultiplexer is also called a data distributor.

#### 1x4 De-Multiplexer

1x4 De-Multiplexer has one input I, two selection lines, s1 & s0 and four outputs Y3, Y2, Y1 &Y0. The

block diagram of 1x4 De-Multiplexer is shown in the following figure.

# PANA ACADEMY

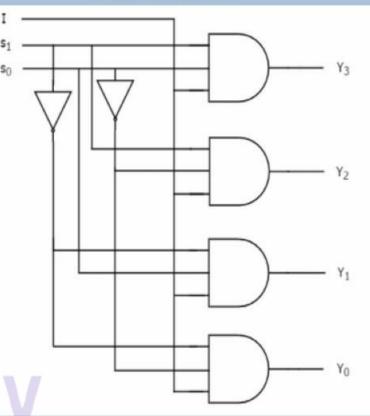

## **DEMULTIPLEXERS (DEMUX)**

31

#### Truth Table

| Selectio       | Selection Inputs |                       | Outputs        |                |                |  |  |

|----------------|------------------|-----------------------|----------------|----------------|----------------|--|--|

| S <sub>1</sub> | S <sub>0</sub>   | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> |  |  |

| 0              | 0                | 0                     | 0              | 0              | 1              |  |  |

| 0              | 1                | 0                     | 0              | 1              | 0              |  |  |

| 1              | 0                | 0                     | 1              | 0              | 0              |  |  |

| 1              | 1                | 1                     | 0              | 0              | 0              |  |  |

From the above Truth table, we can directly write the Boolean functions for each output as

$$Y_3 = s_1 s_0 I$$

$$Y_2 = s_1 s_0{}'I$$

$$Y_1 = s_1{}'s_0I$$

$$Y_0=s_1{}'s_0{}'I$$

#### Logic Diagram

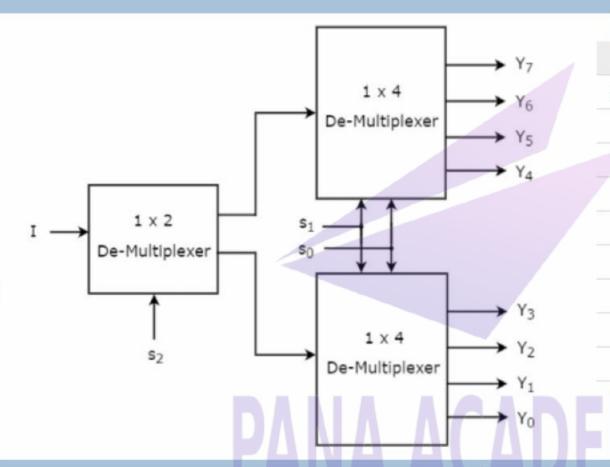

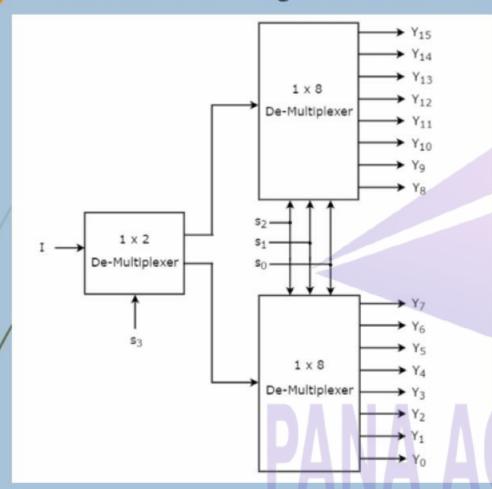

#### IMPLEMENTATION OF HIGHER ORDER DE-MULTIPLEXERS

32

#### 1 X 8 DE-MUX using 1 X 4 and 1 X 2 DE-MUX

#### Truth Table

| Se             | election Inpu  | ıts            |                |                |                | Out            | puts           |                |                |                |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| S <sub>2</sub> | s <sub>1</sub> | s <sub>0</sub> | Y <sub>7</sub> | Y <sub>6</sub> | Y <sub>5</sub> | Y <sub>4</sub> | Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> |

| 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | -1             |

| 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

| 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |

| 0              | 1              | 1              | 0              | 0              | 0              | 0              | ı              | 0              | 0              | 0              |

| 1              | 0              | 0              | 0              | 0              | 0              | T              | 0              | 0              | 0              | 0              |

| 1              | 0              | 1              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              |

| 1              | 1              | 0              | 0              | Ī              | 0              | 0              | 0              | 0              | 0              | 0              |

| 1              | 1              | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

Logic Diagram

#### IMPLEMENTATION OF HIGHER ORDER DE-MULTIPLEXERS

33

#### 1 X 16 DE-MUX using 1 x 8 and 1 x 2 DE-MUX

Logic Diagram

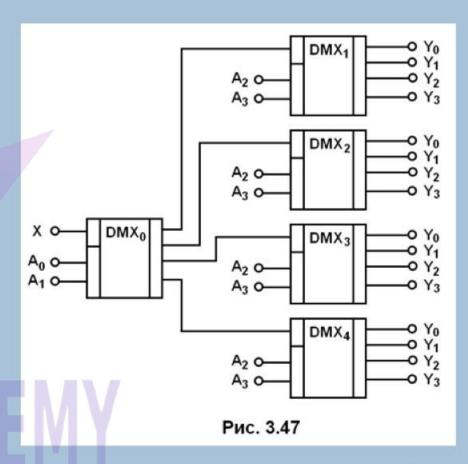

#### 1 X 16 DE-MUX using 1 x 4

$X = INPUT, A_3, A_2, A_1, A_0$  are selection line

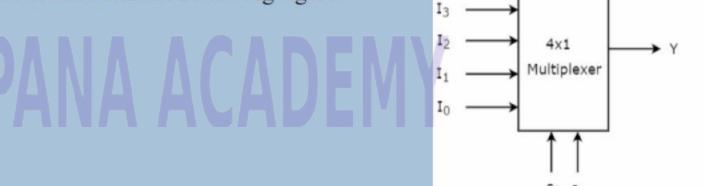

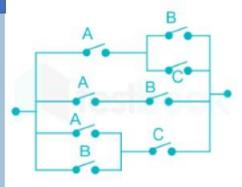

## **MULTIPLEXERS (MUX)**

34

- Multiplexer is a combinational circuit that has maximum of 2<sup>n</sup> data inputs, 'n' selection lines and single output line.

- One of these data inputs will be connected to the output based on the values of selection lines.

- Since there are 'n' selection lines, there will be 2<sup>n</sup> possible combinations of zeros and ones.

- So, each combination will select only one data input. Multiplexer is also called as Mux.

#### 4x1 Multiplexer

4x1 Multiplexer has four data inputs I<sub>3</sub>, I<sub>2</sub>, I<sub>1</sub> & I<sub>0</sub>, two selection lines s<sub>1</sub> & s<sub>0</sub> and one output Y. The block

diagram of 4x1 Multiplexer is shown in the following figure.

Er. Pralhad Chapagain

Truth table of 4x1 Multiplexer is shown below.

| Selection      | n Lines        | Output         |

|----------------|----------------|----------------|

| S <sub>1</sub> | S <sub>0</sub> | Y              |

| 0              | 0              | I <sub>0</sub> |

| 0              | 1              | H              |

| 1              | 0              | I <sub>2</sub> |

| 1              | 1              | l <sub>3</sub> |

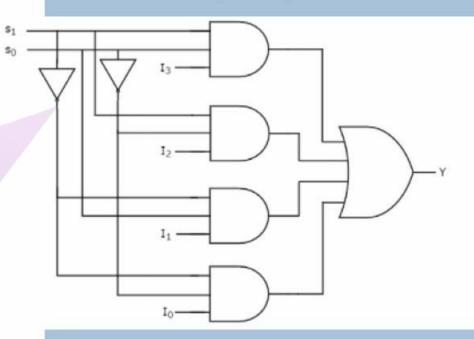

From Truth table, we can directly write the Boolean function for output, Y as

$$Y = S_1{}'S_0{}'I_0 + S_1{}'S_0I_1 + S_1S_0{}'I_2 + S_1S_0I_3$$

#### Logic Diagram

## **MULTIPLEXERS (MUX)**

36

#### **Application**

- Communication system

- Telephone network

- Computer memory

- Transmission from the computer system of a satellite

- Data acquisition system

# PANA ACADEMY

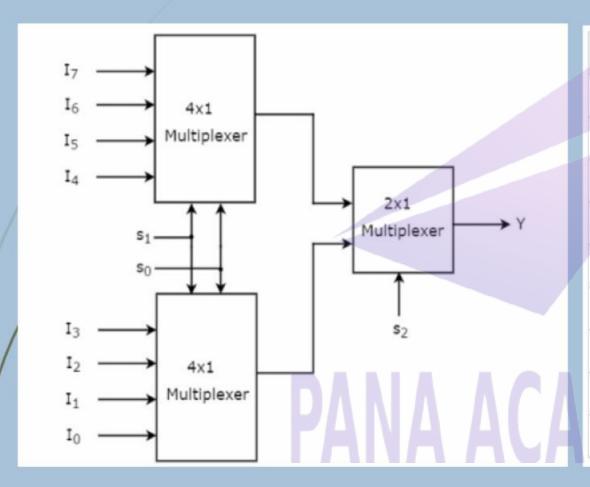

## IMPLEMENTATION OF HIGHER ORDER MULTIPLEXERS

37

#### 8 X 1 MUX using 4 x 1 and 2 x 1 MUX

Truth Table

|                | Selection Inputs | Output         |                |

|----------------|------------------|----------------|----------------|

| S <sub>2</sub> | S <sub>1</sub>   | S <sub>0</sub> | Y              |

| 0              | 0                | 0              | I <sub>0</sub> |

| 0              | 0                | 1              | 11             |

| 0              | 1                | 0              | l <sub>2</sub> |

| 0              | 1                | 1              | l <sub>3</sub> |

| 1              | 0                | 0              | 14             |

| 1              | 0                | 1              | 15             |

| 1              | 1                | 0              | I <sub>6</sub> |

| 1              | 1                | 1              | I <sub>7</sub> |

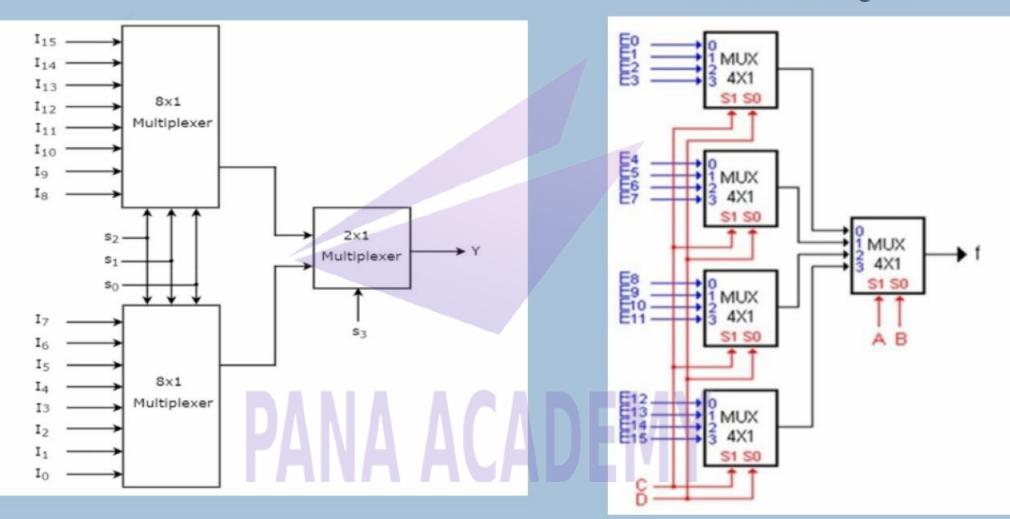

#### IMPLEMENTATION OF HIGHER ORDER MULTIPLEXERS

38

#### 16 X 1 MUX using 8 x 1 and 2 x 1 MUX

#### 16 X 1 MUX using 4 x 1

## **BINARY ADDITION**

| Binary Addi | tion Rules |            |        |

|-------------|------------|------------|--------|

|             |            | Carry Over | Result |

| 1.          | 0 + 0      | 0          | 0      |

| 2.          | 0 +1       | 0          | 1      |

| 3.          | 1+0        | 0          | 1      |

| 4.          | 1+1        | 1          | 0      |

| 5.          | 1+1+1      |            | //\/1  |

| FAA         | AAL        | AVE        | VI V   |

## **BINARY SUBTRACTION**

#### **Rules of Binary Subtraction**

$$\Rightarrow 1 - 0 - 1$$

$$\Rightarrow 1 - 1 = 0$$

$$\Rightarrow 0 - 0 = 0$$

$$\Rightarrow$$

0 - 1 = 1

(This can not be done directly, hence we borrow one digit from the digit to the left or the next higher order digit.)

## **Unsigned Numbers**

As we already know, the unsigned numbers don't have any sign for representing negat numbers. So the unsigned numbers are always positive. By default, the decimal number representation is positive. We always assume a positive sign in front of each decimal digit.

Signed Numbers

The signed numbers have a sign bit so that it can differentiate positive and negative integer numbers. The signed binary number technique has both the sign bit and the magnitude of the number. For representing the negative decimal number, the corresponding symbol in front of the binary number will be added.

The range of numbers that can be represented by n-bits in 2's complement form is  $(-2)^{n-1}$  to  $(2^{n-1})$  -1

Hence, here the smallest number is  $(-2)^7 = -128$ .

### SIGNED AND UNSIGNED BINARY NUMBERS

#### 1. Sign-Magnitude form

In this form, a binary number has a bit for a sign symbol. If this bit is set to 1, the number will be negative else the number will be positive if it is set to 0. Apart from this sign-bit, the n-1 bits represent the magnitude of the number.

#### 2. 1's Complement

By inverting each bit of a number, we can obtain the 1's complement of a number. The negative numbers can be represented in the form of 1's complement. In this form, the binary number also has an extra bit for sign representation as a sign-magnitude form.

#### 3. 2's Complement

By inverting each bit of a number and adding plus 1 to its least significant bit, we can obtain the 2's complement of a number. The negative numbers can also be represented in the form of 2's complement. In this form, the binary number also has an extra bit for sign representation as a sign-magnitude form.

- 1 Which of the following is correct for multiplexer?

- Several inputs and single output

- b) Single input and several outputs

- c) Single input and single output

- d) Several inputs and several outputs

- 2 TDM stands for \_\_\_\_\_

- a) Time direct measurement

- Time division multiplexing

- c) Time direct multiplexing

- d) Time division measurement

- 3 . Multiplexers work with \_\_\_\_\_

- a) Analog signal

- b) Digital signal

- Both analog and digital signal

- d) None of the mentioned

- Which of the following represent multiple input single output switch?

- Multiplexer

- b) De multiplexer

- c) Both multiplexer and demultiplexer

- d) None of the mentioned

- Which of the following is analogous to multiplexer?

Data selector

- b) Data multiplexer

- c) Data filter

- d) None of the mentioned

- 6 Schematic symbol of multiplexer is \_\_\_\_\_

- a) Isosceles triangle

- Isosceles trapezoid

- c) Equilateral triangle

- d) Rectangle

- 7 In digital multiplexer selector line is \_\_\_\_\_

- a) Analog value

- Digital value

- c) Unpredictable

- d) None of the mentioned

- 8 . Which of the following is not a multiplexer?

- a) 8-to-1 line

- b) 16-to-1 line

- c) 4-to-1 line

- 1-to-4 line

- What is a multiplexer?

- a) It is a type of decoder which decodes several inputs and gives one output

- A multiplexer is a device which converts many signals into one

- c) It takes one input and results into many output

- d) It is a type of encoder which decodes several inputs and gives one output

- . The enable input is also known as \_\_\_

- a) Select input

- b) Decoded input

- d) Sink

- 11 . Which combinational circuit is renowned for selecting a single input from multiple inputs

- & directing the binary information to output line?

- Data Selector

- b) Data distributor

- c) Both data selector and data distributor

- d) DeMultiplexer

- 12 What is the function of an enable input on a multiplexer chip?

- a) To apply Vcc

- b) To connect ground

- To active the entire chip

- d) To active one half of the chip

- 13 Which is the major functioning responsibility of the multiplexing combinational circuit?

- a) Decoding the binary information

- b) Generation of all minterms in an output function with OR-gate

- Generation of selected path between multiple sources and a single destination

- d) Encoding of binary information

- 14 One multiplexer can take the place of \_\_\_\_\_

- a) Several SSI logic gates

- b) Combinational logic circuits

- c) Several Ex-NOR gates

- Several SSI logic gates or combinational logic circuits

- A digital multiplexer is a combinational circuit that selects \_\_\_\_\_

One digital information from several sources and transmits the selected one

b) Many digital information and convert them into one

- c) Many decimal inputs and transmits the selected information

- d) Many decimal outputs and accepts the selected information

- 16 In a multiplexer, the selection of a particular input line is controlled by \_\_\_\_\_

- a) Data controller Selected lines

- c) Logic gates

- d) Both data controller and selected lines

- 17 If the number of n selected input lines is equal to 2^m then it requires \_\_\_\_ select lines.

- a) 2

- m

- c) n

- d) 2<sup>n</sup>

- 18. How many select lines would be required for an 8-line-to-1-line multiplexer?

- a) 2

- b) 4

- c) 8

- 3

- 19 . How many NOT gates are required for the construction of a 4-to-1 multiplexer?

- a) 3

- h) 4

- 2

- d) 5

20 On subtracting (01010)2 from (11110)2 using 1's complement, we get \_ a) 01001 b) 11010 c) 10101 10100 On subtracting (001100)2 from (101001)2 using 2's complement, we get a) 1101100 011101 c) 11010101 d) 11010111 On addition of +38 and -20 using 2's complement, we get \_\_\_\_\_ a) 11110001 b) 100001110 010010 d) 110101011

- 23 On subtracting (010110)2 from (1011001)2 using 2's complement, we get \_\_\_\_\_\_

a) 0111001

b) 1100101

- 1000011

- 24 On addition of 28 and 18 using 2's complement, we get \_\_\_\_\_

- a) 00101110

- 0101110

- c) 00101111

- d) 1001111

- On addition of -46 and +28 using 2's complement, we get \_\_\_\_\_

- -10010

- b) -00101

- c) 01011

- d) 0100101

- A decoder converts n inputs to \_\_\_\_\_ outputs

- a) n

- b) n<sup>2</sup>

- 2

- d) n<sup>n</sup>

- Which of the following can be represented for decoder?

- a) Sequential circuit

- Combinational circuit

- c) Logical circuit

- d) None of the mentioned

- 28 Invalid BCD can be made to valid BCD by adding with \_\_\_\_

- a) 0101

- 0110

- c) 0111

- d) 1001

- Which of the following are building blocks of encoders

- a) NOT gate

- OR gate

- c) AND gate

- d) NAND gate

- BCD to seven segment conversion is a \_\_\_

- Decoding process

- b) Encoding process

- c) Comparing process

- d) None of the mentioned

- 31 Decoder is constructed from

- a) Inverters

- b) AND gates

- Inverters and AND gates

- d) None of the mentioned

AND gate EXOR gate combination is \_\_\_\_ If the inputs are P, Q and R, then in the full adder, find the output expression of the sum. 40 1. PORQORR 1. both full and half adder. P XOR Q XOR R 2. full adder 3. PORQANDR half adder 4. PAND QAND R 4. flip flop In full adder, there are 41 39 In a half adder, the carry output is high if the inputs are: 1, 1 Two binary number inputs and two outputs 2. 0.0 Three binary digit inputs and two binary digit outputs 3. 0, 1 Three binary digit inputs and three binary digit outputs 4. 1.0 4. NAND and OR gates

How many number of 2-input NAND gates are required to realise a half adder circuit? Nand 5 -Sum,S Nand) 2. 6 3. 4 Carry, C Nand 4. 8 In half adder, the total number of inputs and outputs are: The following circuit is a: 1. 1, 2 Half subtractor Half adder Full adder 2, 2

Full subtractor

45

For a full Adder

- Sum = AB ⊕ BC ⊕ CA

Carry = A, B, C

- 2. Sum = A, B, C

Carry = A ⊕ B ⊕ C

- 3. Sum =  $A \oplus B \oplus C$ Carry = A, B, C

- Sum =  $A \oplus B \oplus C$ Carry = AB + BC + AC

- 46 In which operation carry is obtained?

a) Subtraction

c) Multiplication

d) Both addition and subtraction

- 4.7 Half-adders have a major limitation in that they cannot \_\_\_\_\_

- a) Accept a carry bit from a present stage

- b) Accept a carry bit from a next stage

Accept a carry bit from a previous stage

- d) Accept a carry bit from the following stages

- 48 If A, B and C are the inputs of a full adder then the carry is given by \_

- A AND B OR (A OR B) AND C

- b) A OR B OR (A AND B) C

- c) (A AND B) OR (A AND B)C

- d) A XOR B XOR (A XOR B) AND C

A half subtractor is an arithmetic circuit which performs subtraction operation on \_\_\_\_\_

input bits.

2. three

- 3. four

- 4. one

- In a half-subtractor circuit with X and Y as inputs, the Borrow (M) and Difference (N = X Y) are given by

4.

$$M = X\overline{Y}, N = \overline{X \oplus Y}$$

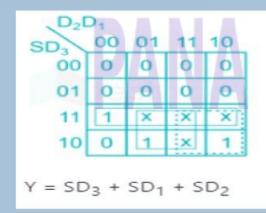

51 Find the Boolean expression for Borrow (B) as the circuit shown below

1.

$$\bar{p}q + \bar{p}r + qr$$

2.

$$pq + pr + qr$$

$$par{q} + pr + ar{q}r$$

4.

$$p\bar{q} + \bar{p}r + \bar{q}r$$

52

What is the circuit?

- 1. Half adder

- 2. Parity generator

- 3. Code convertor

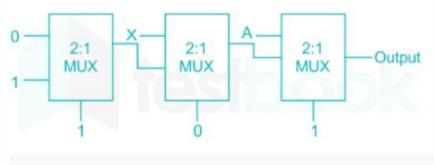

53 Which of the following circuit diagram represents borrow of half subtractor? For subtracting 1 from 0, we use to take a \_\_\_\_\_ from neighbouring bits. a) Carry 4×1 MUX → output Borrow c) Input d) Output 55 The Boolean expression for the output f of the multiplexer shown be 4×1 4×1 output 4×1 MUX → output  $P \oplus Q \oplus R$ ⊕ Q ⊕ R P + Q + R

More than one of the above

The device which changes from serial data to parallel data is:

Demultiplexer

2. Multiplexer

3. Flip-Flop

4. Counter

DANA ACA DE 12 3 MUX - Z

3 MUX - Z

5 6 7 S<sub>2</sub> S<sub>1</sub> S<sub>0</sub>

7 S<sub>2</sub> S<sub>1</sub> S<sub>0</sub>

8 A B C

4 A B C

A 4 × 1 Multiplexer is shown in the Figure below. The output Z is 59 58 Digital multiplexer is basically a combinational logic circuit to perform the operation 1. AND-AND MUX 2. OR-OR AND-OR 1. A NOR C 4. OR-AND 2. B NOR C 3. B XOR C A XOR C

60

The minimum Boolean expression for the following circuit is

AB + AC + BC

- 2. A + BC

- 3. A + B

- 4. A + B + C

Consider the following combinational function block involving four Boolean variables x, y, a, b where x, a, b are inputs and y is the output.

```

f (x, y, a, b)

(

if (x is 1) y = a;

else y = b;

```

Which one of the following digital logic blocks is the most suitable for implementing this function?

- 1. Full adder

- Priority encoder

- . Multiplexer

- 4. Flip-flop

62

The output of the circuit shown is Fig is \_\_\_\_\_

1. 0

3. A

4. 1

| s | D <sub>3</sub> | Dz  | Dη | ×  |

|---|----------------|-----|----|----|

| 0 | -              | × 2 |    | 0  |

| 1 | 0              | 0   | 0  | 0  |

| 1 | 0              | 0   | -1 | 1  |

| 1 | 0              | 1   | 0  | 3  |

| 1 | 1              | 0   | .0 | 15 |

| 1 | 0              | -9  | 1  | ×  |

| 1 | 1              | 0   | 1  | ~  |

63

The combinational circuit shown in the below figure has the function. When selector input 's' is high the circuit is to detect if one of the data lines has logic '1' and no more than one data line is having logic '1', when selector input 'S' is low, the circuit will output '0', regardless of what is on the data lines. The logic of output Y is

$$S(D_1 + D_2 + D_3)$$

2.

$$S\left(\bar{D}_{1}+D_{2}+D_{3}\right)$$

3.

$$\bar{S} (D_1 + D_2) + SD_3$$

4.

$$(D_1 + D_3) + \bar{S} D_2$$

# THANK YOU

# PANA ACADEMY

51 Find the Boolean expression for Borrow (B) as the circuit shown below

1.

$$\bar{p}q + \bar{p}r + qr$$

2.

$$pq + pr + qr$$

$$par{q} + pr + ar{q}r$$

4.

$$p\bar{q} + \bar{p}r + \bar{q}r$$

52

What is the circuit?

- 1. Half adder

- 2. Parity generator

- 3. Code convertor

53 Which of the following circuit diagram represents borrow of half subtractor? For subtracting 1 from 0, we use to take a \_\_\_\_\_ from neighbouring bits. a) Carry 4×1 MUX → output Borrow c) Input d) Output 55 The Boolean expression for the output f of the multiplexer shown be 4×1 4×1 output 4×1 MUX → output  $P \oplus Q \oplus R$ ⊕ Q ⊕ R P + Q + R

More than one of the above

The device which changes from serial data to parallel data is:

Demultiplexer

2. Multiplexer

3. Flip-Flop

4. Counter

DANA ACA DE 12 3 MUX - Z

3 MUX - Z

5 6 7 S<sub>2</sub> S<sub>1</sub> S<sub>0</sub>

7 S<sub>2</sub> S<sub>1</sub> S<sub>0</sub>

8 A B C

4 A B C

A 4 × 1 Multiplexer is shown in the Figure below. The output Z is 59 58 Digital multiplexer is basically a combinational logic circuit to perform the operation 1. AND-AND MUX 2. OR-OR AND-OR 1. A NOR C 4. OR-AND 2. B NOR C 3. B XOR C A XOR C

60

The minimum Boolean expression for the following circuit is

AB + AC + BC

- 2. A + BC

- 3. A + B

- 4. A + B + C

Consider the following combinational function block involving four Boolean variables x, y, a, b where x, a, b are inputs and y is the output.

```

f (x, y, a, b)

(

if (x is 1) y = a;

else y = b;

```

Which one of the following digital logic blocks is the most suitable for implementing this function?

- 1. Full adder

- Priority encoder

- . Multiplexer

- 4. Flip-flop

62

The output of the circuit shown is Fig is \_\_\_\_\_

1. 0

3. A

4. 1

| s | D <sub>3</sub> | Dz  | Dη | ×  |

|---|----------------|-----|----|----|

| 0 | -              | × 2 |    | 0  |

| 1 | 0              | 0   | 0  | 0  |

| 1 | 0              | 0   | -1 | 1  |

| 1 | 0              | 1   | 0  | 3  |

| 1 | 1              | 0   | .0 | 15 |

| 1 | 0              | -9  | 1  | ×  |

| 1 | 1              | 0   | 1  | ~  |

63

The combinational circuit shown in the below figure has the function. When selector input 's' is high the circuit is to detect if one of the data lines has logic '1' and no more than one data line is having logic '1', when selector input 'S' is low, the circuit will output '0', regardless of what is on the data lines. The logic of output Y is

$$S(D_1 + D_2 + D_3)$$

2.

$$S\left(\bar{D}_{1}+\ D_{2}\ +\ D_{3}\right)$$

3.

$$\bar{S} (D_1 + D_2) + SD_3$$

4.

$$(D_1 + D_3) + \bar{S} D_2$$

# 2. Digital Logic and Microprocessor

PANA ACADEMY

Er. Pralhad Chapagain

# Syllabus

- 2.1 Digital logic: Number Systems, Logic Levels, Logic Gates, Boolean algebra, Sum-of-Products Method, Product-of-Sums Method, Truth Table to Karnaugh Map. (AExE0201)

- 2.2 Combinational and arithmetic circuits: Multiplexetures, Demultiplexetures, Decoder, Encoder, Binary Addition, Binary Subtraction, operation on Unsigned and Signed Binary Numbers. (AExE0202)

- 2.3 Sequential logic circuit: RS Flip-Flops, Gated Flip-Flops, Edge Triggered Flip-Flops, Mater- Slave Flip-Flops. Types of Registers, Applications of Shift Registers, Asynchronous Counters, Synchronous Counters.

(AExE0203)

- 2.4 Microprocessor: Internal Architecture and Features of microprocessor, Assembly Language Programming.

(AExE0204)

- 2.5 Microprocessor system: Memory Device Classification and Hierarchy, Interfacing I/O and Memory Parallel Interface. Introduction to Programmable Peripheral Interface (PPI), Serial Interface, Synchronous and Asynchronous Transmission, Serial Interface Standards. Introduction to Direct Memory Access (DMA) and DMA Controllers.

(AEXE0205)

- 2.6 Interrupt operations: Interrupt, Interrupt Service Routine, and Interrupt Processing. (AExE0206)

2.3 Sequential logic circuit: RS Flip-Flops, Gated Flip-Flops, Edge Triggered Flip-Flops, Mater- Slave Flip-Flops. Types of Registers, Applications of Shift Registers, Asynchronous Counters, Synchronous Counters. (AExE0203)

# PANA ACADEMY

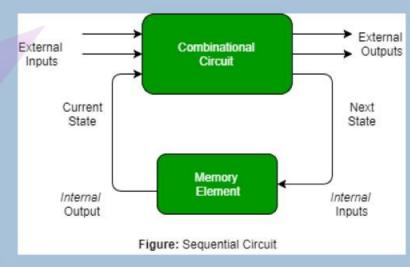

#### SEQUENTIAL LOGIC

5

- Sequential circuit produces an output based on current input and previous input variables.

- That means sequential circuits include memory elements which are capable of storing binary information.

- That binary information defines the state of the sequential circuit at that time.

- A latch is capable of storing one bit of information.

- As shown in figure there are two types of input to the combinational logic:

- External inputs which not controlled by the circuit.

- Internal inputs which are a function of a previous output states.

PANA ACADEMY

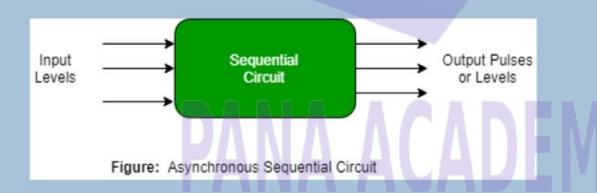

#### Asynchronous sequential circuit

- These circuit do not use a clock signal but uses the pulses of the inputs.

- These circuits are faster than synchronous sequential circuits because they change their state immediately when there is a change in the input signal.

- We use asynchronous sequential circuits when speed of operation is important and independent of internal clock pulse.

- But these circuits are more difficult to design and their output is uncertain.

#### **SEQUENTIAL LOGIC - TYPES**

7

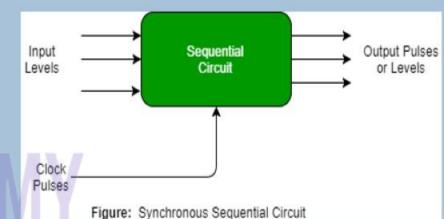

#### Synchronous sequential circuit

- These circuit uses clock signal and level inputs (or pulsed) with restrictions on pulse width and circuit propagation.

- The output pulse is the same duration as the clock pulse for the clocked sequential circuits.

- Since they wait for the next clock pulse to arrive to perform the next operation, so these circuits are bit slower compared to asynchronous.

- Level output changes state at the start of an input pulse and remains in that until the next input or clock pulse.

- We use synchronous sequential circuit in synchronous counters, flip flops, and in the design of state management machines.

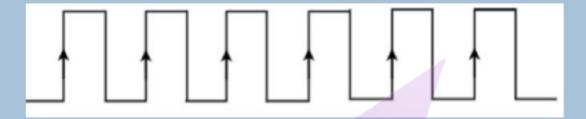

#### **CLOCK SIGNAL AND TRIGGERING**

#### 8 Clock signal:

- Clock signal is a periodic signal and its ON time and OFF time need not be the same.

- We can represent the clock signal as a square wave, when both its ON time and OFF time are same.

- The pattern repeats with some time period. In this case, the time period will be equal to either twice of ON time or twice of OFF time.

- We can represent the clock signal as train of pulses, when ON time and OFF time are not same

- In this case, the time period will be equal to sum of ON time and OFF time.

#### **CLOCK SIGNAL AND TRIGGERING**

#### 7 Types of Triggering

- Level triggering

- Edge triggering

#### Level triggering

- There are two levels, namely logic High and logic Low in clock signal.

- Following are the two types of level triggering.

- Positive level triggering

- Negative level triggering

■ If the sequential circuit is operated with the clock signal when it is in Logic High, then that type of triggering is known as **Positive level triggering**. It is highlighted in above figure.

If the sequential circuit is operated with the clock signal when it is in Logic Low, then that type of triggering is known as **Negative level triggering**. It is highlighted in the following figure.

#### Edge triggering

- There are two types of transitions that occur in clock signal. That means, the clock signal transitions either from Logic Low to Logic High or Logic High to Logic Low..

- Positive edge triggering

- Negative edge triggering

- If the sequential circuit is operated with the clock signal that is transitioning from Logic Low to Logic High, then that type of triggering is known as Positive edge triggering. It is also called as rising edge triggering. It is shown in the following figure.

#### **CLOCK SIGNAL AND TRIGGERING**

If the sequential circuit is operated with the clock signal that is transitioning from Logic High to Logic Low, then that type of triggering is known as Negative edge triggering. It is also called as falling edge triggering. It is shown in the following figure.

There are two types of memory elements based on the type of triggering that is suitable to operate it.

- Latches

- Flip-flops

- Latches operate with enable signal, which is level sensitive. Whereas, flip-flops are edge sensitive.

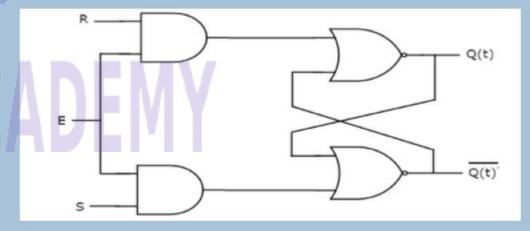

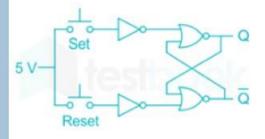

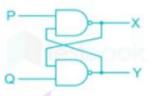

#### SR Latch

- SR Latch is also called as Set Reset Latch.

- This latch affects the outputs as long as the enable, E is maintained at '1'. The circuit diagram of SR Latch

is shown in the following figure

| S | R | Q t+1 |

|---|---|-------|

| 0 | 0 | Q t   |

| 0 | 1 | 0     |

| 1 | 0 | 1     |

| 1 | 1 | 120   |

Er. Pralhad Chapagain

#### **FLIP-FLOP**

13

Flip-flop is a basic digital memory circuit, which stores one bit of information.

- Flip flops are the fundamental blocks of most sequential circuits.

- Flip-flops are used as memory elements in clocked sequential circuit.

- Flip-flop circuit has two outputs, one for the normal value and one for the complement value of the bit stored in it.

- Binary information can be enter a flip-flop in a variety of ways, a fact, which gives rise to different types

of flip-flops.

- SR Flip-Flop

- D Flip-Flop

- JK Flip-Flop

- T Flip-Flop

# PANA ACADEMY

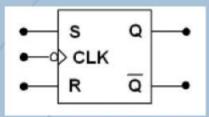

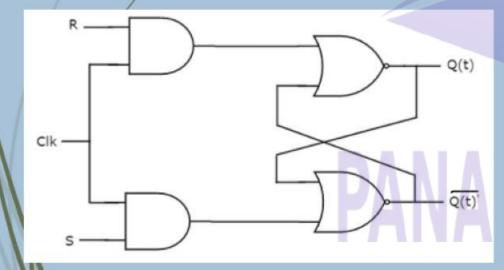

SR (Set-Reset) flip-flop operates with only positive clock transitions or negative clock transitions.

Whereas, SR latch operates with enable signal. The circuit diagram of SR flip-flop is shown in the

following figure.

Graphical Symbol

Logic diagram

| Clock    | S | R | Q(t) | Q(t+1) | Comment       |

|----------|---|---|------|--------|---------------|

| ↓ ↓      | 0 | 0 | 0    | 0      | Hold          |

| 1        | 0 | 0 | 1    | 1      | Hold          |

| ↓ ·      | 0 | 1 | 0    | 0      | Reset         |

| 1        | 0 | 1 | 1    | 0      | Reset         |

| <b>1</b> | 1 | 0 | 0    | 1      | Set           |

| <b>1</b> | 1 | 0 | 1    | 1      | Set           |

| 1        | 1 | 1 | 0    | X      | Indeterminant |

| ↓ ↓      | 1 | 1 | 1    | X      | Indeterminant |

Characteristic Table

#### FLIP-FLOP – SR FLIP-FLOP

15

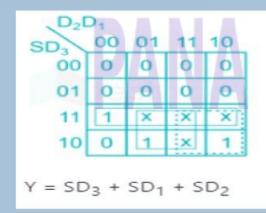

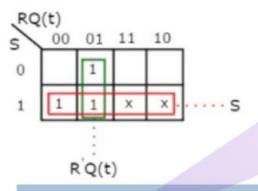

K-Map for next state, Q t+1 is shown in the following figure.

| SR Flip-flop |        |   |   |  |  |  |

|--------------|--------|---|---|--|--|--|

| Q(t)         | Q(t+1) | S | R |  |  |  |

| 0            | 0      | 0 | X |  |  |  |

| 0            | 1      | 1 | 0 |  |  |  |

| 1            | 0      | 0 | 1 |  |  |  |

| 1            | 1      | X | 0 |  |  |  |

**Excitation Table**

$$Q\left(t+1\right)=S+R'Q\left(t\right)$$

K-MAP and Boolean function

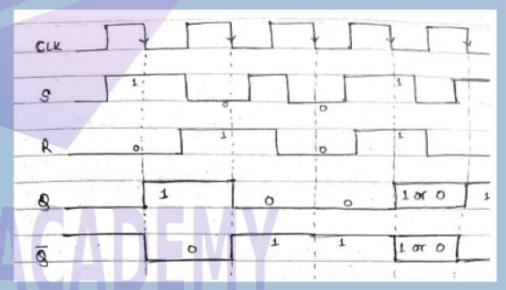

Timing diagram

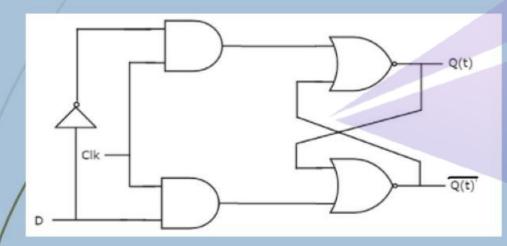

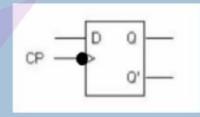

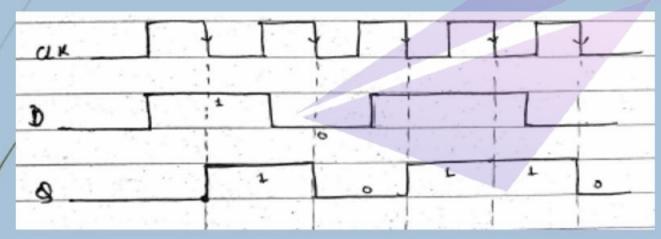

- D (Data) flip-flop operates with only positive clock transitions or negative clock transitions. Whereas, D latch operates with enable signal.

- That means, the output of D flip-flop is insensitive to the changes in the input, D except for active transition of the clock signal. The circuit diagram of D flip-flop is shown in the following figure.

Logic diagram

Graphical Symbol

| Clock  | D | Q(t) | Q(t+1) | Comment |

|--------|---|------|--------|---------|

| J      | 0 | 0    | 0      | Reset   |

| ↓<br>↓ | 0 | 1    | 0      | Reset   |

| Ţ      | 1 | 0    | 1      | Set     |

| 1      | 1 | 1    | 1      | Set     |

Characteristic Table

17

$$Q(t+1) = D$$

Boolean function

|      | D Flip-flop |   |

|------|-------------|---|

| Q(t) | Q(t+1)      | D |

| 0    | 0           | 0 |

| 0    | 1           | 1 |

| 1    | 0           | 0 |

| 1    | 1           | 1 |

**Excitation Table**

Timing diagram

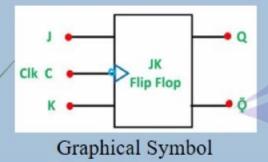

#### FLIP-FLOP – JK FLIP-FLOP

- 18

- JK flip-flop is the modified version of SR flip-flop.

- It operates with only positive clock transitions or negative clock transitions. The circuit diagram of JK flip-flop is shown in the following figure.

- The indeterminant state of RS flip-flop is defined in JK flip-flop.

| Clock    | J | K | Q(t) | Q(t+1) | Comment    |

|----------|---|---|------|--------|------------|

| <b>1</b> | 0 | 0 | 0    | 0      | Hold       |

| <b>\</b> | 0 | 0 | 1    | 1      | Hold       |

| 1        | 0 | 1 | 0    | 0      | Reset      |

| 1        | 0 | 1 | 1    | 0      | Reset      |

| <b>1</b> | 1 | 0 | 0    | 1      | Set        |

| 1        | 1 | 0 | 1    | 1      | Set        |

| 1        | 1 | 1 | 0    | 1      | Complement |

| J        | 1 | 1 | 1    | 0      | Complement |

Characteristic Table

Logic diagram

Er. Pralhad Chapagain

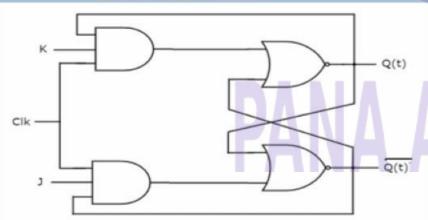

#### FLIP-FLOP – JK FLIP-FLOP

Three variable K-Map for next state, Q ig(t+1ig) is shown in the following figure.

$$Q\left(t+1\right)=JQ\left(t\right)'+K'Q\left(t\right)$$

K-MAP and Boolean function

| JK flip-flop |        |   |   |  |  |

|--------------|--------|---|---|--|--|

| Q(t)         | Q(t+1) | J | K |  |  |

| 0            | 0      | 0 | x |  |  |

| 0            | 1      | 1 | x |  |  |

| 1            | 0      | X | 1 |  |  |

| 1            | 1      | X | 0 |  |  |

#### **Excitation Table**

Timing diagram

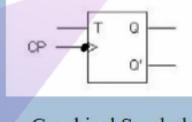

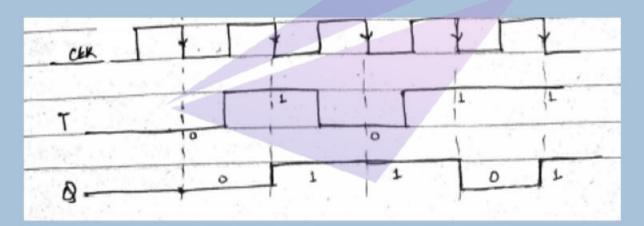

#### FLIP-FLOP - T FLIP-FLOP

The T flipflop is a single input version of the JK flipflop.

Logic diagram

- The T flipflop is obtained from JK type if both inputs are tied together.

- The designation T comes from the ability of the flipflop to "Toggle", or change state. Regardless of the present state of the flipflop, it assumes the complement state when the clock pulse occurs while input T is in logic 1.

Graphical Symbol

|        |             | Clock    | T | Q(t)  | Q(t+1)         |     |

|--------|-------------|----------|---|-------|----------------|-----|

| Q(t)   |             | <b>1</b> | 0 | 0     | 0              |     |

| cik—   | $\Lambda I$ | 1        | 0 | 1     | 1              |     |

|        | AN          | Ţ        | 1 | 0     | 1              |     |

| T Q(t) |             | ↓        | 1 | 1     | 0              |     |

|        |             |          |   | Chara | ecteristic Tab | ile |

Er. Pralhad Chapagain

Characteristic Table

Comment

Hold

Hold

Complement

Complement

21

From the above characteristic table, we can directly write the next state equation as

$$Q(t+1) = T'Q(t) + TQ(t)'$$

$$\Rightarrow Q(t+1) = T \oplus Q(t)$$

| T flip-flop |        |   |  |  |  |

|-------------|--------|---|--|--|--|

| Q(t)        | Q(t+1) | Т |  |  |  |

| 0           | 0      | 0 |  |  |  |

| 0           | 1      | 1 |  |  |  |

| 1           | 0      | 1 |  |  |  |

| 1           | 1      | 0 |  |  |  |

#### Boolean function

#### **Excitation Table**

# Timing diagram

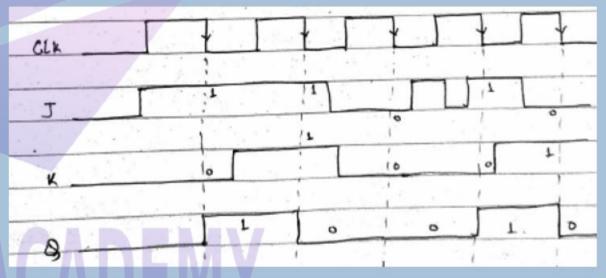

#### Race Around Condition In JK Flip-flop

- ► For J-K flip-flop, if J=K=1, and if clk=1 for a long period of time, then Q output will toggle as long as CLK is high, which makes the output of the flip-flop unstable or uncertain.

- This problem is called race around condition in J-K flip-flop.

- This problem (Race Around Condition) can be avoided by ensuring that the clock input is at logic "1" only for a very short time.

- To eliminate race around condition:

- Use edge- triggered flip-flop

- Use Master Slave JK flip flop.

# PANA ACADEMY

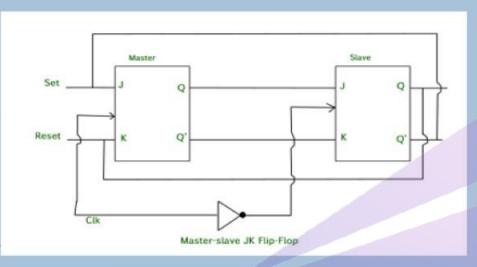

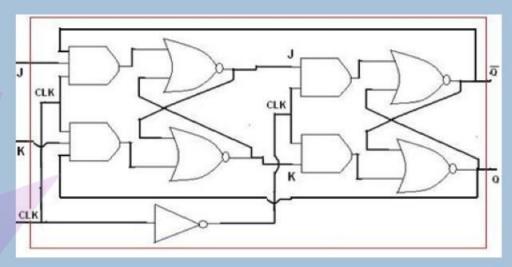

#### MASTER – SLAVE JK FLIPFLOP

#### 23

#### Master Slave JK flip flop

- The Master-Slave Flip-Flop is basically a combination of two JK flip-flops connected together in a series configuration.

- Out of these, one acts as the "master" and the other as a "slave".

- The output from the master flip flop is connected to the two inputs of the slave flip flop whose output is fed back to inputs of the master flip flop.

- In addition to these two flip-flops, the circuit also includes an inverter.

- The inverter is connected to clock pulse in such a way that the inverted clock pulse is given to the slave flip-flop.

- In other words if CP=0 for a master flip-flop, then CP=1 for a slave flip-flop and if CP=1 for master flip flop then it becomes 0 for slave flip flop.

#### Block diagram

Logic diagram

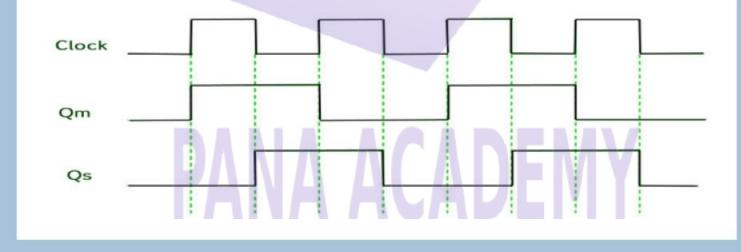

#### Timing diagram

Er. Pralhad Chapagain

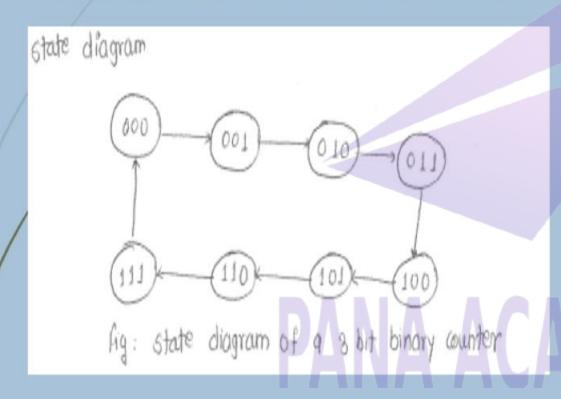

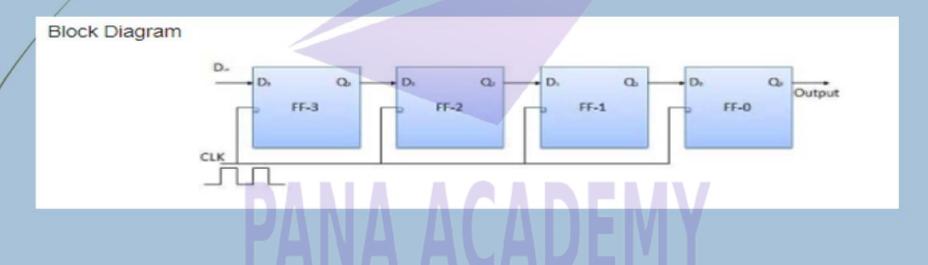

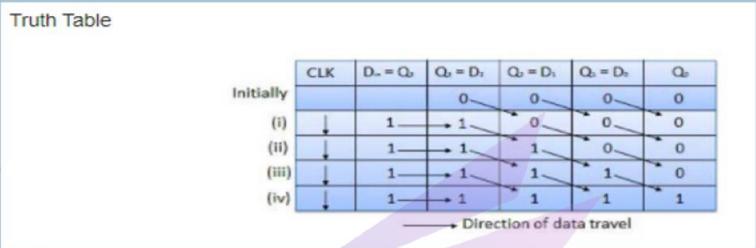

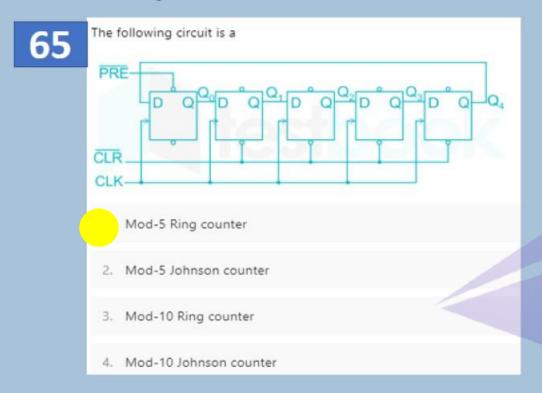

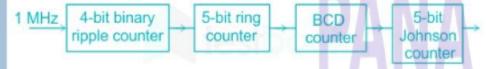

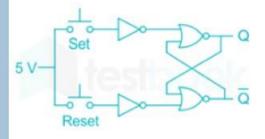

## **COUNTERS**

- 25 Counter is a sequential circuit.

- A digital circuit which is used for a counting pulses is known counter.

- Counter is the widest application of flip-flops. It is a group of flip-flops with a clock signal applied.

- Counters are of two types.

- Asynchronous or ripple counters.

- In asynchronous counter we don't use universal clock, only first flip flop is driven by main clock and the clock input of rest of the following flip flop is driven by output of previous flip flops

#### Synchronous counters.

- Unlike the asynchronous counter, synchronous counter has one global clock which drives each flip flop so output changes in parallel.

- The one advantage of synchronous counter over asynchronous counter is, it can operate on higher frequency than asynchronous counter as it does not have cumulative delay because of same clock is given to each flip flop

## SYNCHRONOUS VS ASYNCHRONOUS COUNTERS

| •          |                                      |                                                                      |                                                                                     |

|------------|--------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Sr.<br>No. | Parameter                            | Asynchronous counter                                                 | Synchronous counter                                                                 |

| 1.         | Circuit<br>complexity                | Logic circuit is simple.                                             | With increase in number of states, the logic circuit becomes complicated.           |

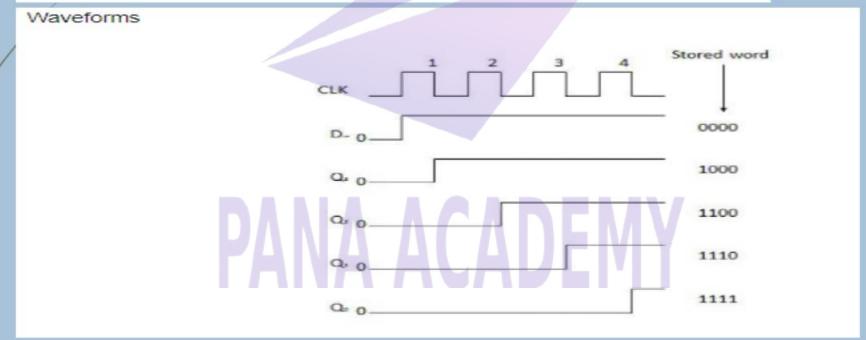

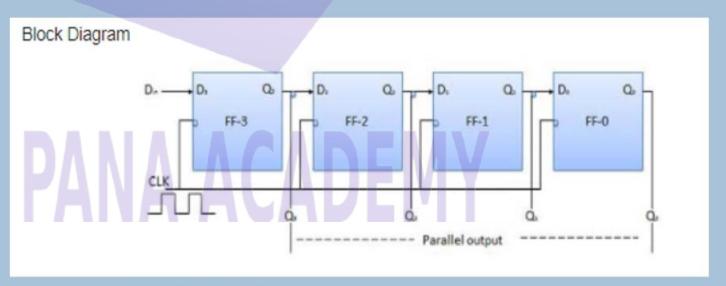

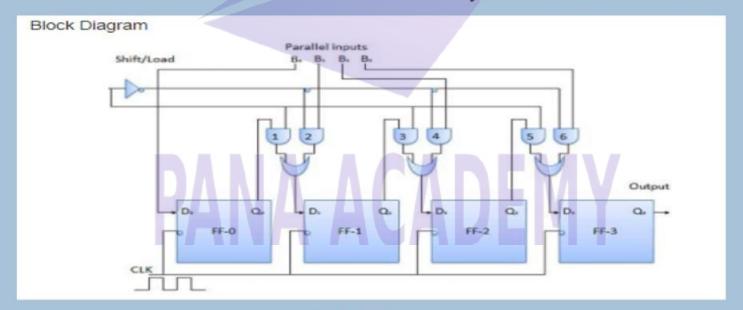

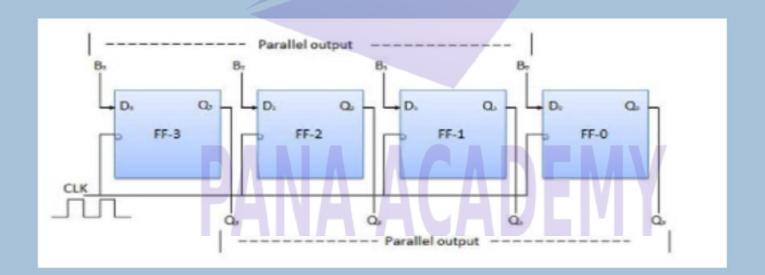

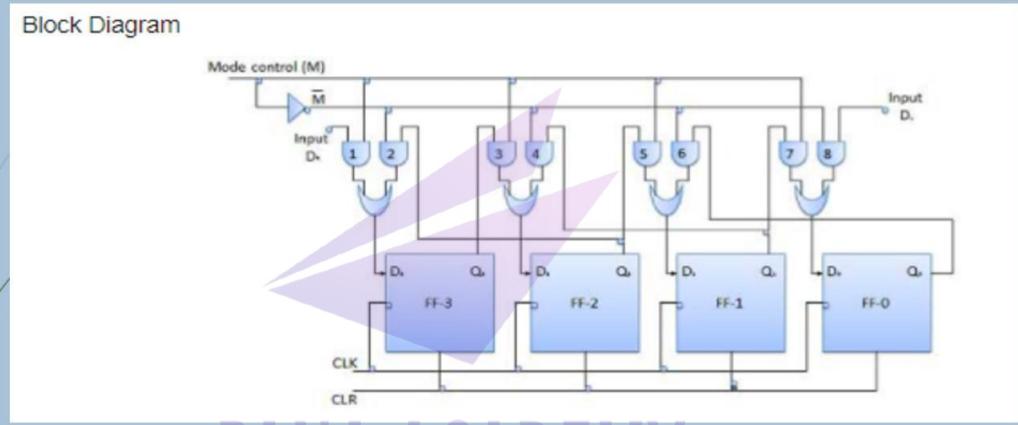

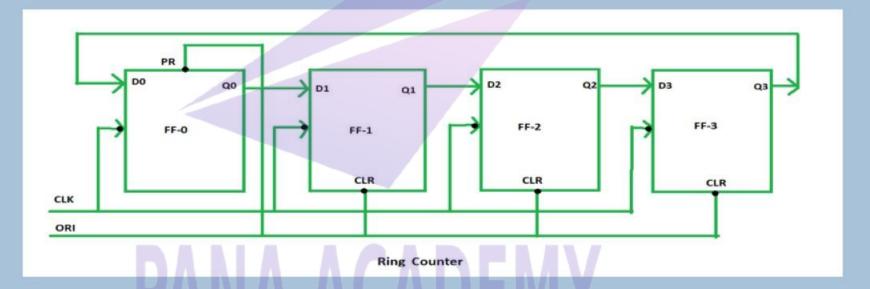

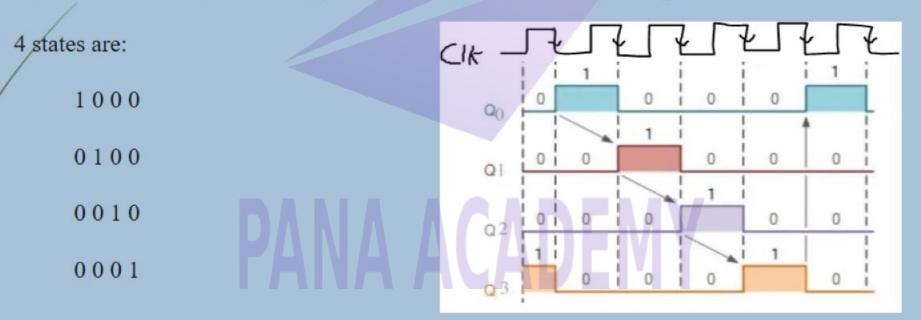

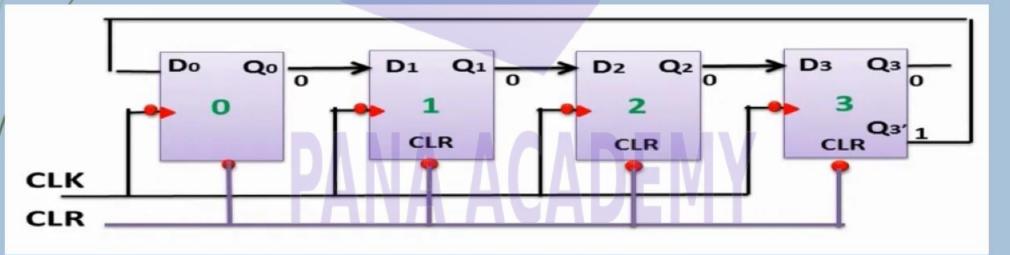

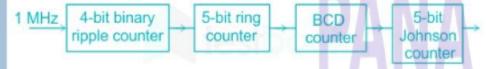

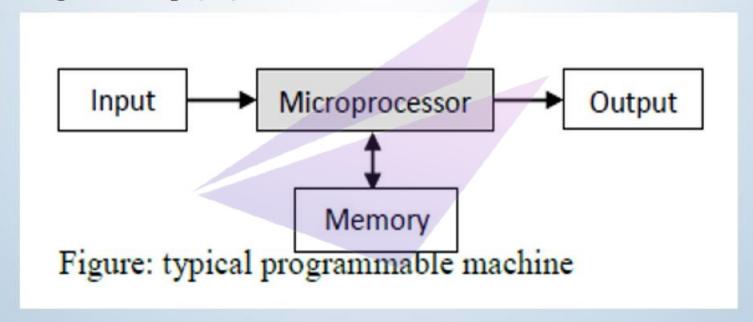

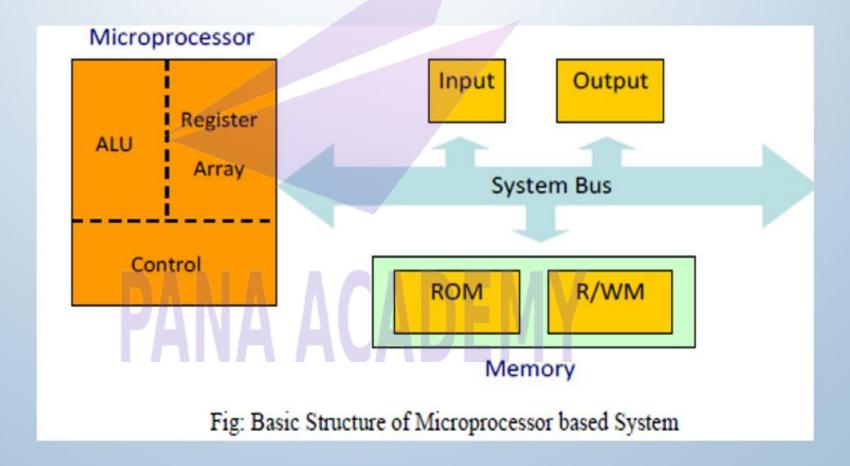

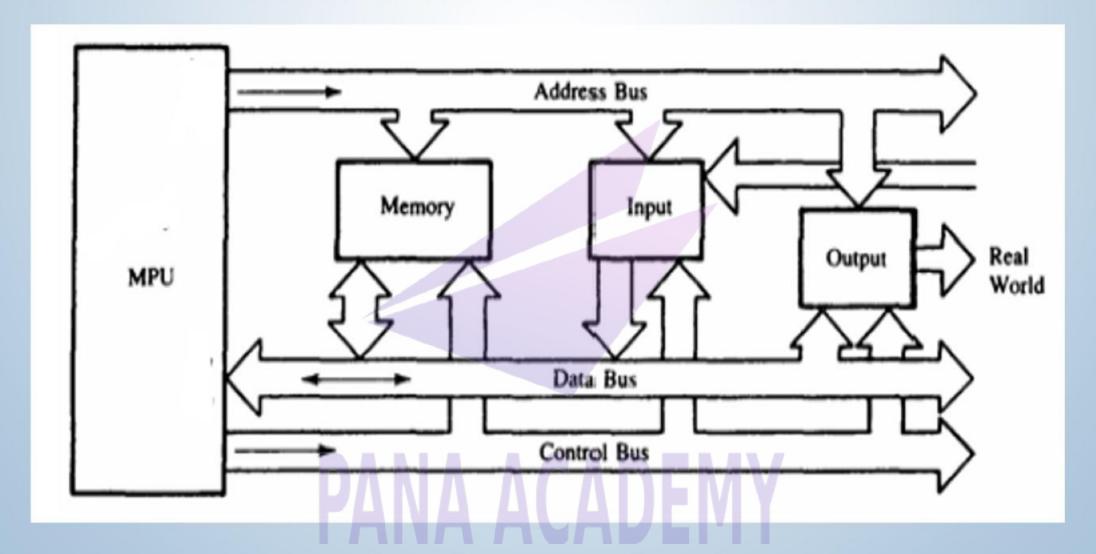

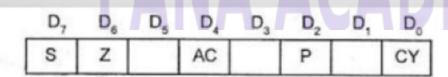

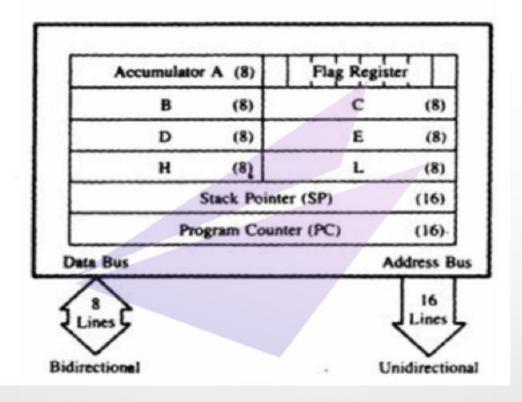

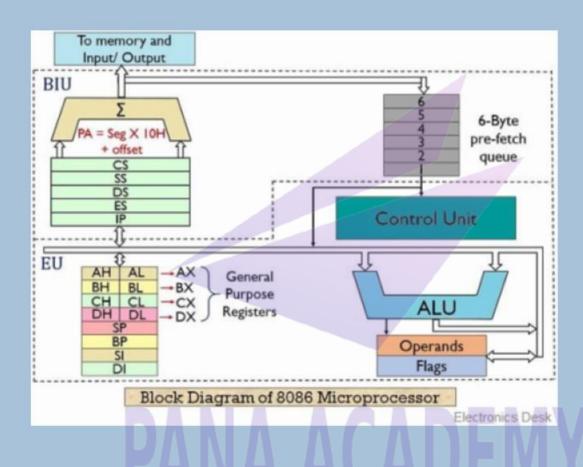

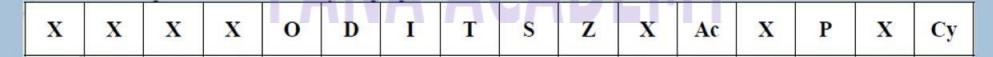

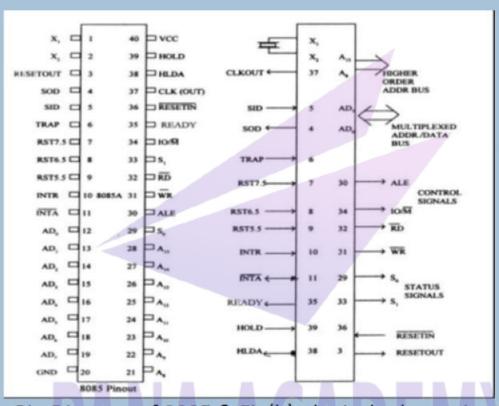

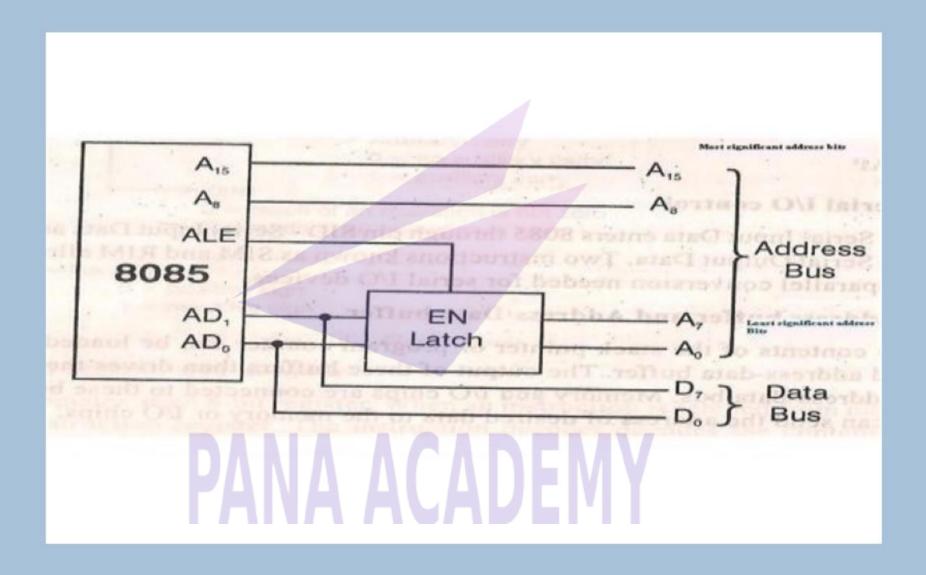

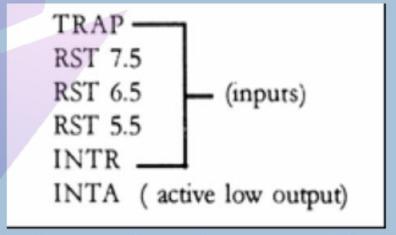

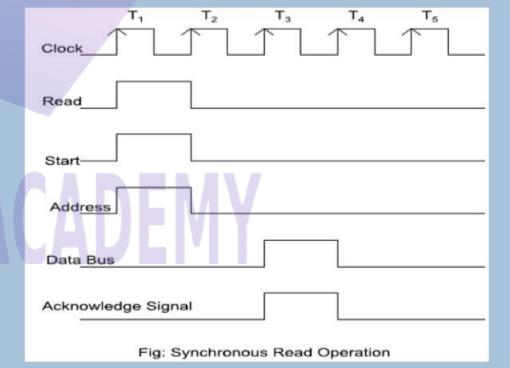

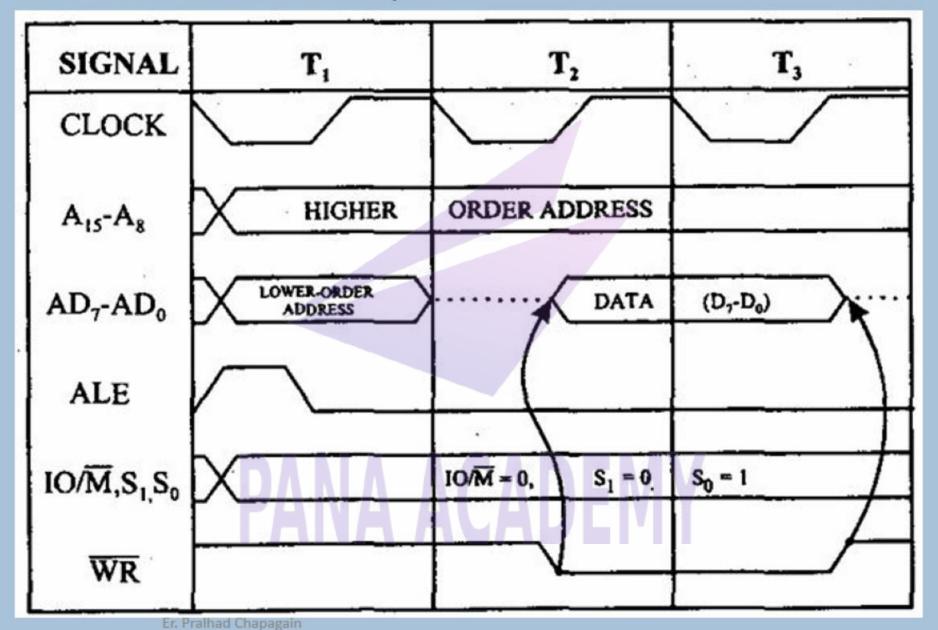

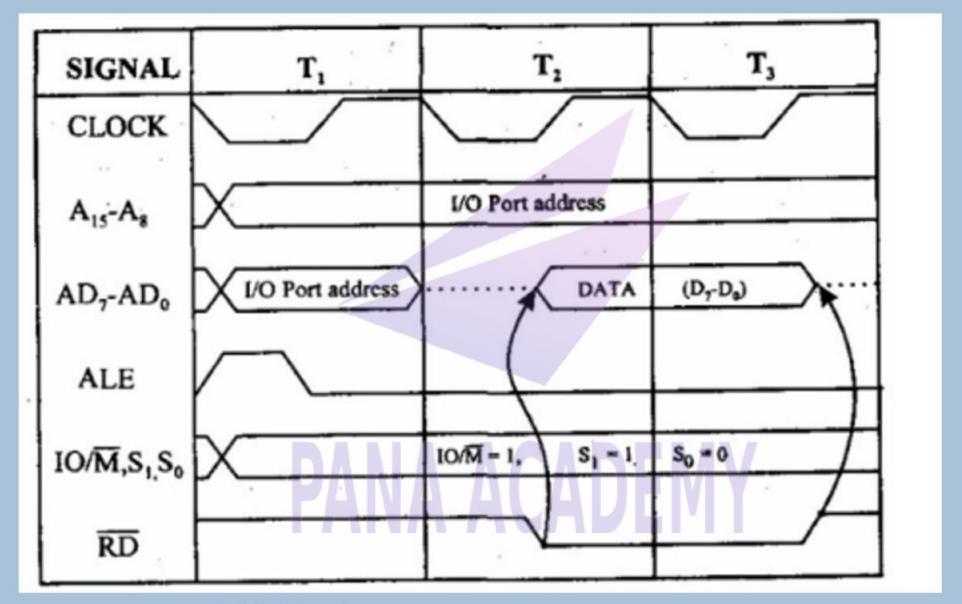

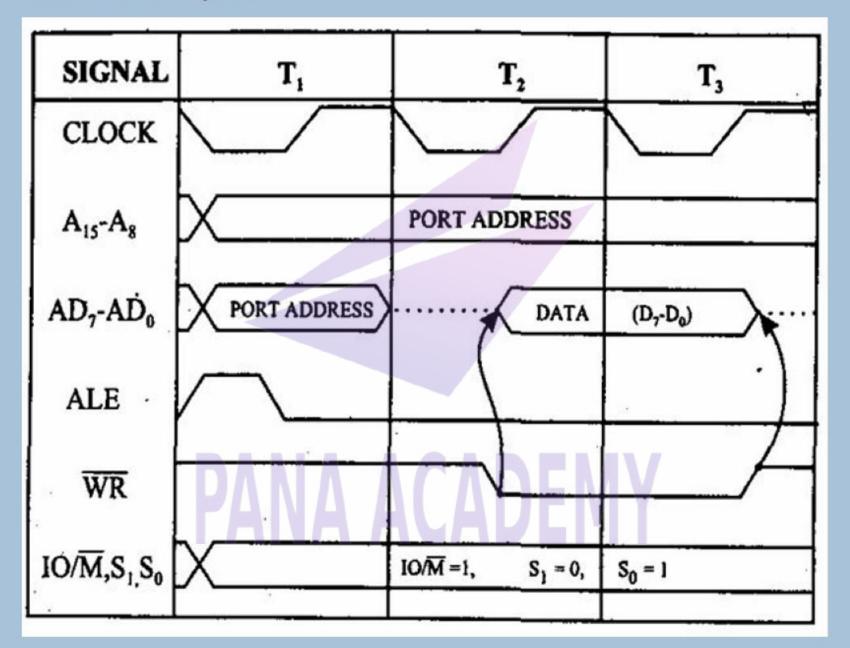

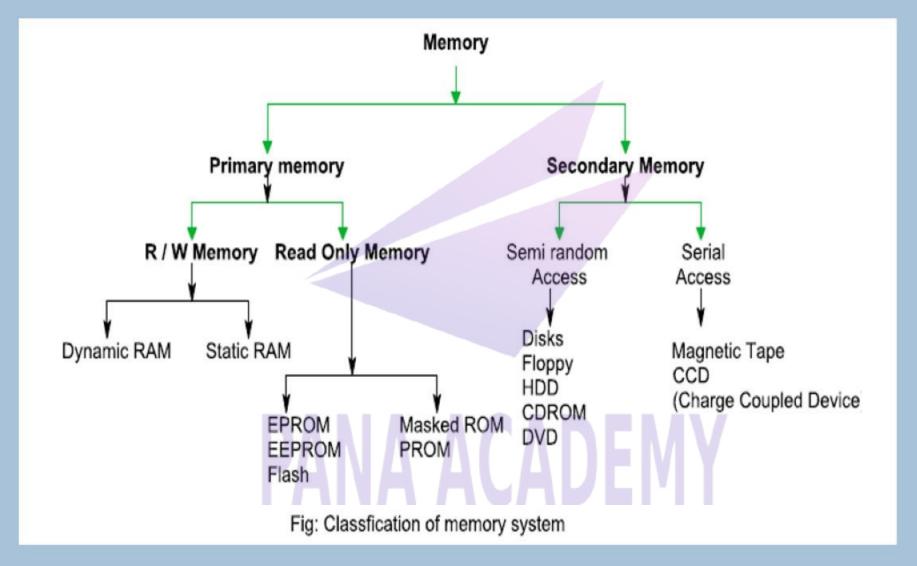

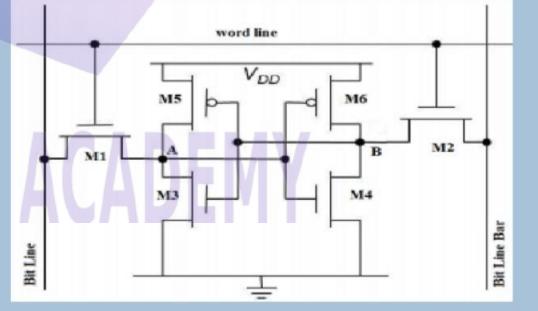

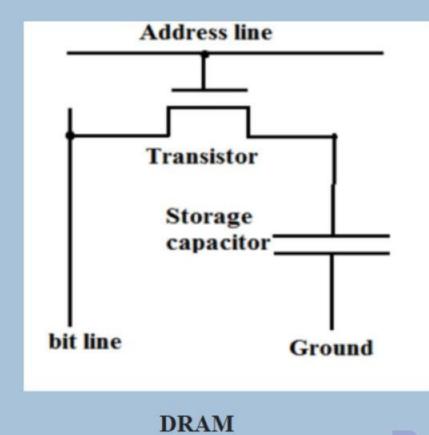

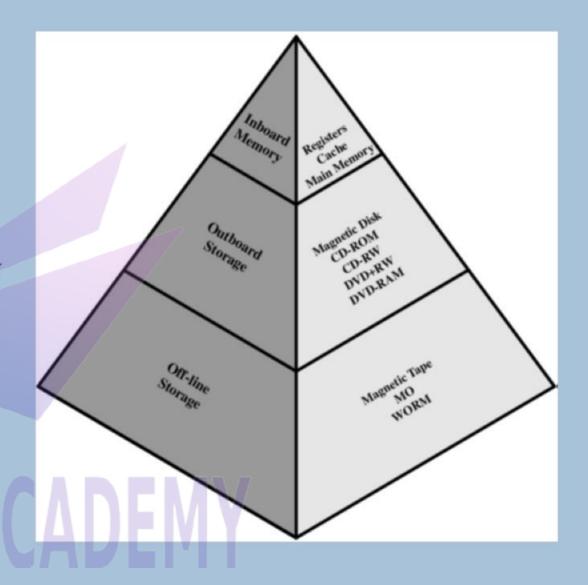

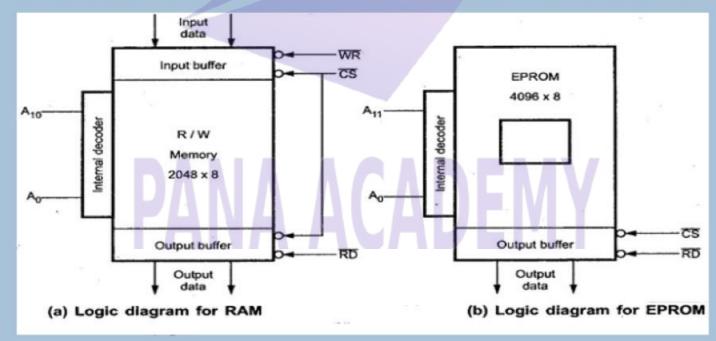

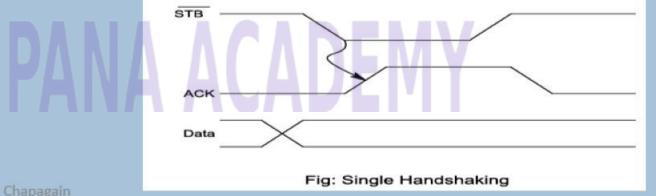

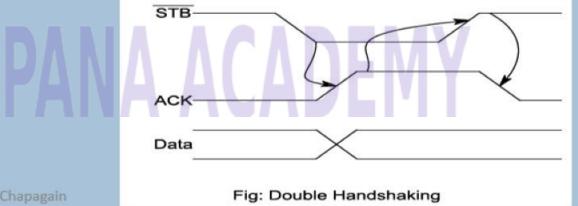

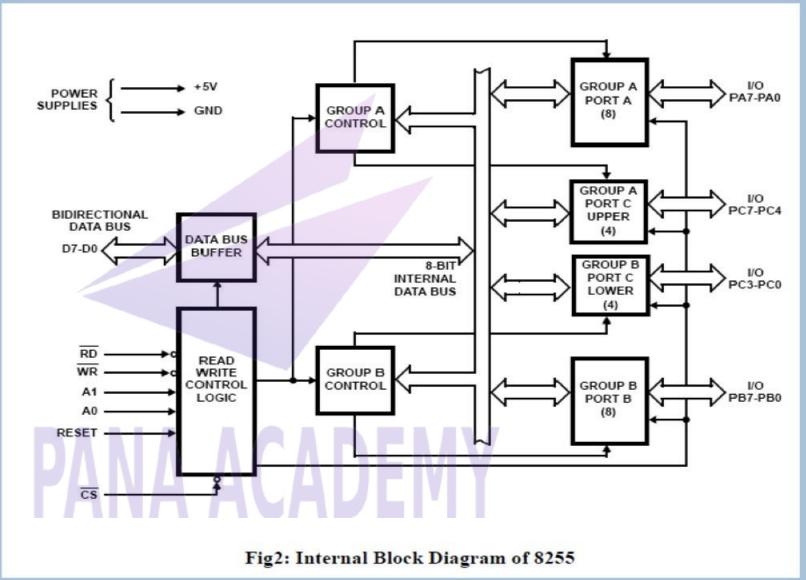

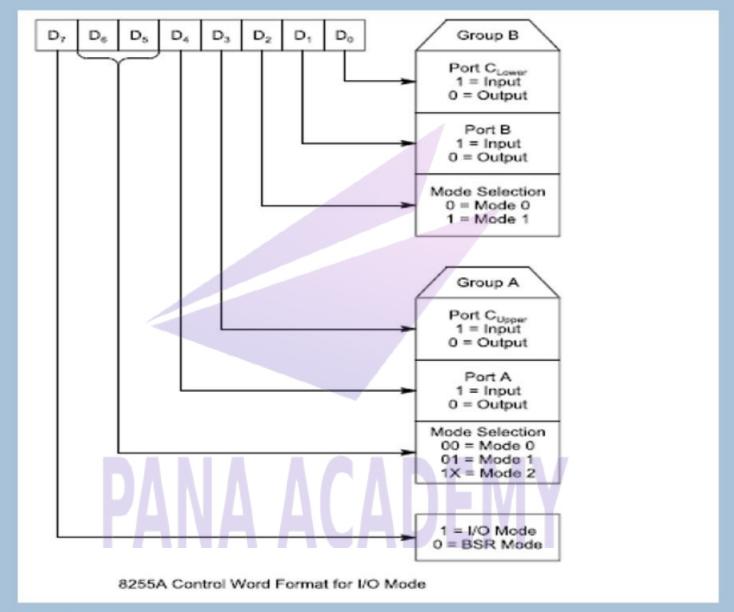

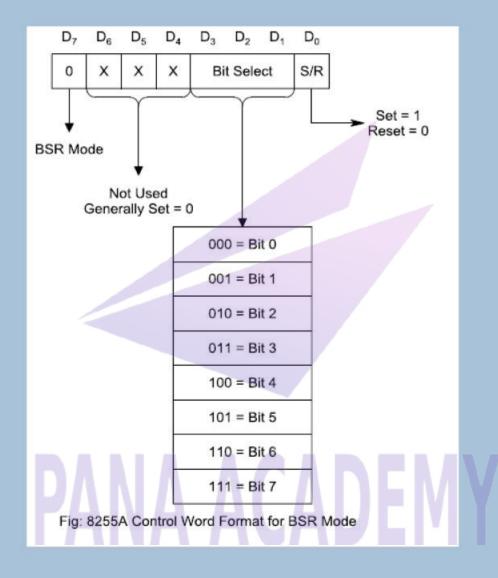

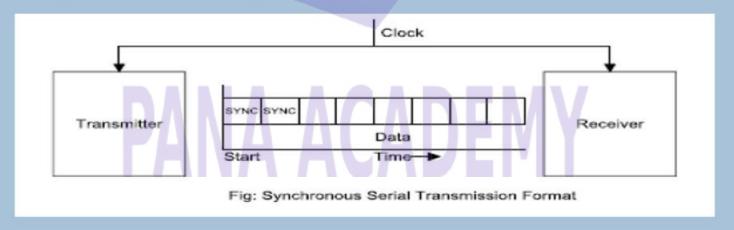

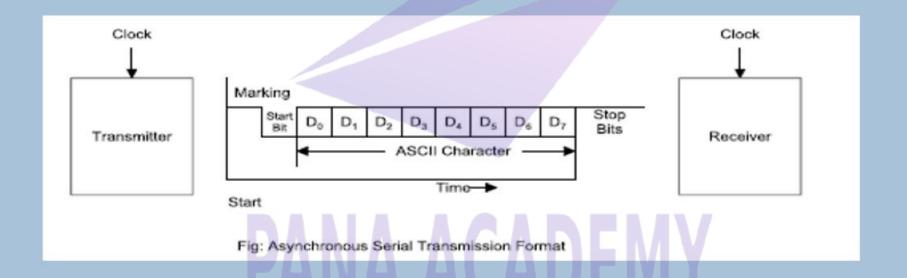

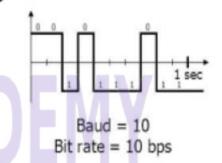

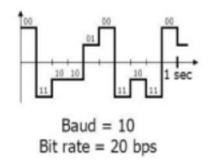

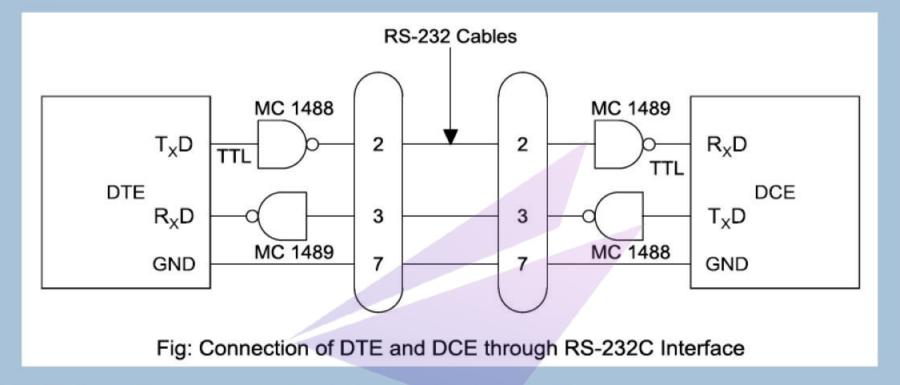

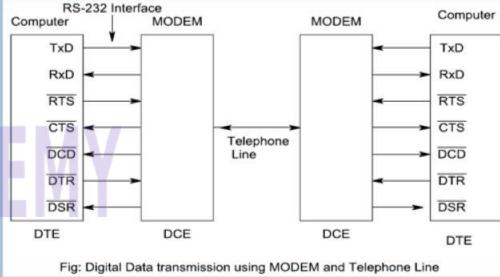

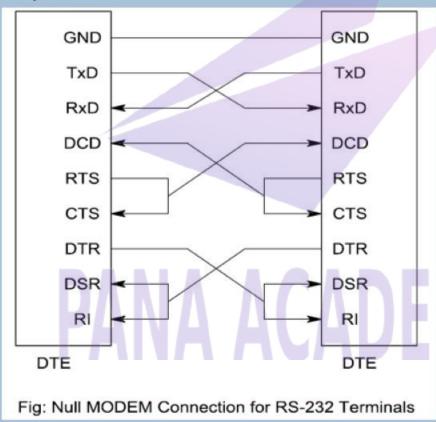

| 2.         | Connection<br>pattern                | Output of the preceding FF, is connected to clock of the next FF.    | There is no connection<br>between output of<br>preceding FF and CLK of<br>next one. |